ขบวนการออกแบบวงจรด้วย HDL

US Department of Defend (กระทรวงกลาโหมของสหรัฐอเมริกา หรือเรียกย่อๆว่า DOD) ได้บังคับว่า hardware ที่สร้าง ให้กับ DOD ต้องใช้ HDL ที่เรียกว่า VHDLในการอธิบายการออกแบบ โดย VHDL จะมีรูปแบบมาจากภาษาโปรแกรม ADA (ซึ่งเป็น ภาษาบังคับของDOD ในการเขียนโปรแกรม Software) ดังนั้นบริษัททั้งหลายที่ต้องการจะทำสัญญาออกแบบ hardware ให้กับ DOD จึงฝึกวิศวกรให้ใช้ VHDL

ในปีคศ. 1985 Phil Moorby จาก บริษัท Gateway Design Automation ได้สร้างโปรแกรมที่ช่วยในการออกแบบ digital hardware เรียกว่า Verilog-XL ขึ้น โดยผู้ออกแบบวงจรสารมารถอธิบายวงจรได้โดยใช้ HDL ซึ่งเรียกว่า Verilog ภายหลัง บริษัท Gateway Design Automation ได้กลายเป็นส่วนหนึ่งของ บริษัท Cadence Design System ในปีคศ. 1989 และ บริษัท Cadence ได้ยก Verilog HDL ให้เป็นของสาธารณะ (Public Domain) ทำให้มีผู้นำไปพัฒนาเพิ่มขึ้น และใช้กันอย่างแพร่หลาย จนในที่สุดได้มีการจัดตั้ง IEEE1364 มาตรฐานสำหรับ Verilog HDL ขึ้น และมีองค์กรที่ไม่หวังผลกำไรชื่อ Open Verilog International (OVI) ดูแลให้ Verilog HDL เป็นไปตามมาตรฐานนี้

ในปัจจุบัน จะมี "ภาษา" Verilog HDL เพียงหนึ่งเดียว แต่มีโปรแกรมที่ Simulate

ภาษานี้มากมาย ในหลาย Platform ไม่ว่าจะเป็น Unix, PC (DOS & Windows) และ

Macintosh อาจกล่าวได้ว่า ในวงการ EDA (Electronic Design Automation)

VerilogHDL เป็นเครื่องมือ ที่มีผู้ใช้มากที่สุด (ส่วน VHDL นั้นเป็นที่นิยมในยุโรป

)

สำหรับ PC มีโปรแกรม Verilog Simulatorอยู่มากมายเช่น VeriBest, Viper, SILOS,

Veriwell โปรแกรมเหล่านี้มีความแตกต่างในเรื่องของความเร็วและ Feature ของการใช้งาน

แต่จะใช้ Description ของ Verilog HDL เดียวกัน (แน่นอนอาจมีจุดต่างกันบ้างเช่นเดียวกับภาษา

C แต่ละบริษัทอาจมี Lib. ต่างกัน)

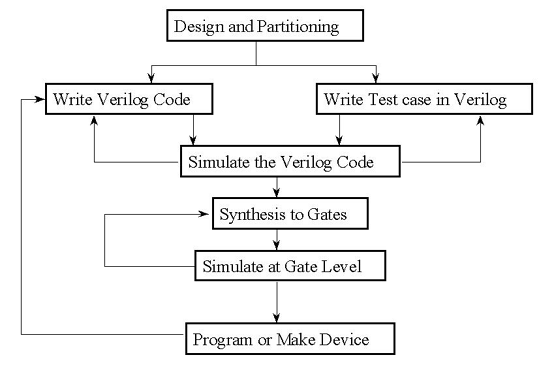

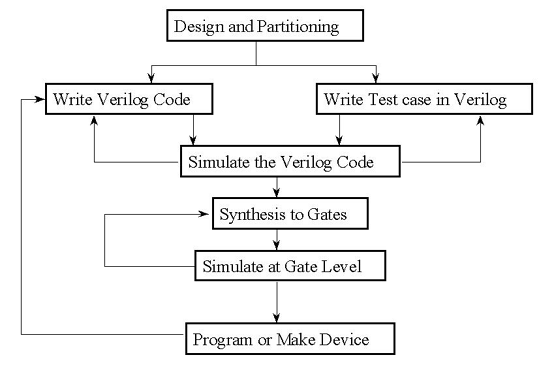

ขบวนการออกแบบวงจรด้วย HDL

|

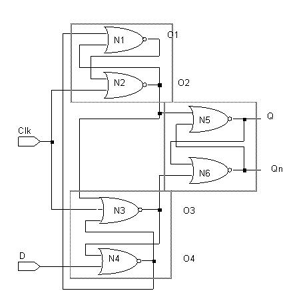

วงจรทางด้านซ้ายมือเป็นวงจรของ negative edge trigger D-flip flop

ที่สร้างโดยใช้ NOR gate ต่อกันทั้งหมด 6 gates ในการเขียน Verilog แบบ Structure

จะเป็นการบรรยายว่า input ของ NOR2 ต่อกับ output ของ NOR1 และ ต่อกับ input

Clk ฯลฯ ดังตัวอย่าง Verilog code

|

// Negative Edge-Triggered D FF |

ตัวอย่างการออกแบบวงจร negative edge trigger D flip-flop

และเป็นวงจรที่ ทำงานเช่นเดียวกับ วงจรข้างบน ดังนั้น port ต่างๆ ของวงจร (module)

จึงเหมือนกัน สังเกตุว่า Q และ Qn ถูกประกาศเป็น reg ทั้งนี้เนื่องจาก Q และ Qn ไม่ใช่ ouput ของ gate แต่จะมีการกำหนด ค่าให้ Q และ Qn (จะอธิบายภายหลัง) Code กำหนดการทำงานว่า ทุกครั้งที่มี negative edge ของสัญญาณ Clk เกิดขึ้นหลังจากนั้น 1 timeunit "ค่า" ของQเปลี่ยนเป็นDและ "ค่า" ของ compliment ของ D แต่ถ้าไม่มี negative edge ของสัญญาณ Clk เกิดขึ้น Q และ Qn ไม่เปลี่ยนแปลง |

Q=D; |

<== ทั้ง Q และ Qn ต้องเก็บค่าได้ ดังนั้นเวลาsynthesis

จะได้ latch หรือ flip=flop สำหรับ Q และ Qn หมายความว่า ใช้ flip-flop2 อันเพื่อสร้าง

D flip-flop 1 อัน |

| ตัวอย่างของ code ที่ simulate ได้ แต่ synthesis ไม่ได้ delay เมื่อเขียน code ว่า a= #10 b+c; หมายความว่า adder มี propagationdelay = 10 timeunit ซึ่งใช้เพื่อการ simulate แต่ในตอน synthesis ไม่สามารถสร้างวงจรให้มีdelayเป็น 10 ได้ delay ของ adder ที่จะถูกสร้าง ขึ้นอยู่กับ วงจร และ technology ที่ใช้ delay มีไว้เพื่อการ simulate เท่านั้น เพื่อดู timing ของการทำงาน synthesisor ทั่วไปจะไม่สนใจ delayที่อยู่ใน code การหาร (/) เมื่อใช้การหารใน expressionตอน simulate ย่อมสามารถหาผลลัพธ์ได้ แต่ในการ synthesis วงจรหารไม่ใช่วงจรมาตรฐาน synthesisor ส่วนใหญ่ไม่สามรถจะสร้างวงจรหารได้เอง synthesisor บางอันสามารถทำการหารได้ถ้าเป็นก่รหารด้วยเลขยกกำลังของ 2 (2,4,8...) เนื่องจากจะไปใช้วงจร shift left แทน |