# การทำนายข้อมูลใช้ซ้ำเพื่อเลี่ยงการบันทึกแคช

นางสาววริษา ศรีไตรรัตนรักษ์

วิทยานิพนธ์นี้เป็นส่วนหนึ่งของการศึกษาตามหลักสูตรปริญญาวิศวกรรมศาสตรดุษฎีบัณฑิต สาขาวิชาวิศวกรรมคอมพิวเตอร์ ภาควิชาวิศวกรรมคอมพิวเตอร์ คณะวิศวกรรมศาสตร์ จุฬาลงกรณ์มหาวิทยาลัย ปีการศึกษา 2558 ลิขสิทธิ์ของจุฬาลงกรณ์มหาวิทยาลัย

# DATA REUSABILITY PREDICTION FOR CACHE BYPASSING

Miss Warisa Sritriratanarak

A Dissertation Submitted in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy Program in Computer Engineering

Department of Computer Engineering

Faculty of Engineering

Chulalongkorn University

Academic Year 2015

Copyright of Chulalongkorn University

| By                | MissWarisa Sritriratanarak                                                                        |  |

|-------------------|---------------------------------------------------------------------------------------------------|--|

| Field of Study    | Computer Engineering                                                                              |  |

| Thesis Advisor    | Professor Prabhas Chongstitvatana, Ph.D.                                                          |  |

| Thesis Co-advisor | Assistant Professor Mongkol Ekpanyapong, Ph.D.                                                    |  |

|                   | ne Faculty of Engineering, Chulalongkorn University in Partial quirements for the Doctoral Degree |  |

|                   |                                                                                                   |  |

| THESIS COMMITT    | EE                                                                                                |  |

|                   |                                                                                                   |  |

|                   | Chairman                                                                                          |  |

|                   | (Assistant Professor Sukree Sinthupinyo, Ph.D.)                                                   |  |

|                   |                                                                                                   |  |

|                   | Thesis Co-advisor                                                                                 |  |

|                   | (Assistant Professor Mongkol Ekpanyapong, Ph.D.)                                                  |  |

|                   | Examiner (Assistant Professor Krerk Piromsopa, Ph.D.)                                             |  |

|                   | External Examiner                                                                                 |  |

|                   | (Assistant Professor Kemathat Vibhatavanij, Ph.D.)                                                |  |

Thesis Title DATA REUSABILITY PREDICTION FOR CACHE BYPASSING

วริษา ศรีไตรรัตนรักษ์ : การทำนายข้อมูลใช้ซ้ำเพื่อเลี่ยงการบันทึกแคช (Data Reusability Prediction for Cache Bypassing) อ. ที่ปรึกษาวิทยานิพนธ์หลัก : ศ.ดร. ประภาส จงสถิตย์วัฒนา, อ. ที่ปรึกษาวิทยานิพนธ์ร่วม : ผศ.ดร.มงคล เอกปัญญาพงศ์, 72 หน้า.

การปรับปรุงหน่วยความจำแคชด้วยวิธีบายพาสเป็นวิธีเพิ่มสมรรณะสำหรับหน่วย

ความจำแคชระดับสุดท้ายในหน่วยประมวลผลหลายแกนซึ่งข้อมูลส่วนใหญ่ไม่เคยถูกนำกลับมาใช้ใหม่

อย่างไรก็ตามเทคนิคการสร้างทางลัดเกือบทั้งหมดพึ่งพาแต่วิธีอย่างใดอย่างหนึ่งโดยเฉพาะ เช่น การ

ใช้ตัวนับและตาราง ทำให้ไม่สามารถแก้ปัญหาการมีงานที่สลับชับช้อนของตัวประมวลผลหลายแกนได้

วิทยานิพนธ์ฉบับนี้เสนอวิธีทางเลือกโดยการทำนายผลของการทำบายพาสโดยใช้ชัพพอร์ตเวคเตอร์แม

ชชีน โดยใช้การเก็บข้อมูลที่ถูกเรียกใช้จากหน่วยประมวลผลโดยโปรแกรมจำลองการทำงานของ

หน่วยประมวลผลหลายแกน ซึ่งข้อมูลที่ได้จะทำมาฝึกการเรียนรู้ด้วยเครื่องจักรที่เรียกว่าชัพพอร์ต

เวคเตอร์แมชชีน ผลลัพธ์ที่ได้คือตัวทำนายการบายพาสที่เหมาะสมสำหรับตัวประมวลผลหลายแกน

ซัพพอร์ตเวคเตอร์แมชชีนจะตัดสินว่าข้อมูลแต่ละตัวจะถูกเก็บลงในหน่วยความจำแคชหรือไม่ แล้วทำ

การวัดผลด้วยโปรแกรมจำลองการทำงานของหน่วยความจำแคชเพื่อวัดประสิทธิภาพของหน่วย

ความจำแคชว่าดีขึ้นเพียงใด ผลของการทดลองแสดงให้เห็นว่าเมื่อตั้งพารามิเตอร์ที่เหมาะสมให้กับชัพ

พอร์ตเวคเตอร์แมชชีน จะสามารถสร้างแบบจำลองเพื่อตัดสินใจเก็บข้อมูลหรือปล่อยผ่านข้อมูลได้เป็น

อย่างดี และสามารถเพิ่มอัตราการเข้าถึงข้อมูลแล้วพบได้ 5.34% ภายใต้โปรแกรมวัดค่าสแปลชทู

| ภาควิชา : วิศวกรรมคอมพิวเตอร์ | ลายมือชื่อนิสิต                       |

|-------------------------------|---------------------------------------|

| สาขาวิชา: วิศวกรรมคอมพิวเตอร์ | ลายมือชื่อ อ.ที่ปรึกษาวิทยานิพนธ์หลัก |

|                               |                                       |

## 5371814921: MAJOR COMPUTER ENGINEERING

KEYWORDS: CACHE MEMORY / CACHE BYPASSING/ SUPPORT VECTOR MACHINE

WARISA SRITRIRATANARAK: DATA REUSABILITY PREDICTION FOR CACHE BYPASSING. ADVISOR: PROF. PRABHAS CHONGSTITVATANA, Ph.D., CO-ADVISOR: ASST. PROF. MONGKOL EKPANYAPONG, Ph.D., 72 pp.

Cache bypassing emerged as a performance improvement method for shared Last-Level Caches (LLC) in multicore processors where large portions of data are never reused. However, most bypass techniques have relied on ad hoc methods such as counters and tables which can not tackle the complexity of multicore workloads. In this dissertation, we propose an alternative method to predict cache bypassing using Support Vector Machine (SVM) models. Based on access traces obtained from representative benchmarks running on the Multi2Sim simulator, supervised SVM training was performed in order to obtain a bypass prediction model suitable for LLC in multi-core processors. The SVM outputs bypassing classifiers which are integrated on the simulator to quantify LLC performance improvements. Results show that, with appropriate parameters and kernel functions, SVM is capable of generating bypassing models which improve LLC performance on multicore processors, achieving an average 5.34% hit rate improvement across SPLASH2 benchmark combinations.

| Department : Computer Engineering     | Student's Signature    |

|---------------------------------------|------------------------|

| Field of Study : Computer Engineering | Advisor's Signature    |

| Academic Year:                        | Co-advisor's Signature |

# Acknowledgements

A PhD dissertation is a hard proof of patience and perseverance of a person dedicated with their life. This work could never be accomplished without a kind guidance from my adviser, Prof. Prabhas Chongstitvatana. My deepest gratitude is always expressed towards him. Also, I am sincerely grateful to my co-supervisor, Asst. Prof. Mongkol Ekpanyapong, for his informative guidance and support throughout my Ph.D. candidature. My dissertation would not be completed without his insightful and knowledgeable suggestions. I am truly proud that I was under their supervision.

I greatly appreciate Asst. Prof. Sukree Sinthupinyol, Asst. Prof. Krerk Piromsopa, and Asst. Prof. Kemathat Vibhatavanij, for being in my dissertation committee and giving many useful comments and suggestions to improve my dissertation.

Many thanks are due to all Intelligent System Laboratory's members and all Ph.D. fellows for their discussions and contributions to research works. And to all my dear friends who understand a Phd's life and always so supportive.

I would like to thank Department of Computer Engineering for the opportunity and meaningful experience. During my time at this department, I have learned an important lesson: Patience and effort are the most important things during a hard time.

Last but not least, this long journey could never be completed without the support from my lovely family whom enjoyed my not-so-schedule work hours and exploited them extensively. Also my life partner, Paulo, who dedicated himself to enlighten me during those depressive hours and let me know the limit of his patience is endless. This dissertation is dedicated to them.

# Contents

| Pag                                   | e, |

|---------------------------------------|----|

| $f Abstract \ (Thai) \ldots \ldots$ i | V  |

| Abstract (English)                    | v  |

| Acknowledgements                      | √i |

| Contents                              | ii |

| List of Tables                        | Х  |

| List of Figures                       | κi |

| Chapter                               |    |

| Introduction                          | 1  |

| 1.1 Objectives of Research            | 5  |

| 1.2 Scopes of Study                   | 5  |

| 1.3 Summary of Contributions          | 6  |

| 1.4 Dissertation Organization         | 6  |

| I Background                          | 7  |

| 2.1 Cache                             | 7  |

| 2.1.1 Cache Organization              | 7  |

| 2.1.2 Cache Replacement Policy        |    |

| 2.1.3 Cache Writes                    |    |

| 2.1.4 Multilevel cache                |    |

| 2.1.5 Cache Consistency               |    |

| 2.2 Machine Learning                  |    |

| II Literature Reviews                 | 5  |

| 3.1 Cache Partitioning                |    |

| 3.2 Cache Replacement Policy          |    |

| 3.3 Cache Prefetching                 |    |

| 3.4 Cache Bypassing                   |    |

| 5.4 Cache Bypassing                   | U  |

| V Methodology                         | 4  |

| 4.1 The offline process               | 5  |

| 4.1.1 Preparing data                  | 5  |

| 4.1.2 The simulator                   | 5  |

| Chapter                               | age |

|---------------------------------------|-----|

| 4.1.3 Benchmarks                      | 26  |

| 4.1.4 The training data               | 27  |

| 4.1.5 Features and Kernel Functions   | 28  |

| 4.2 The online process                | 29  |

| 4.3 The implementation considerations | 30  |

|                                       |     |

| Results and discussion                | 31  |

| 5.1 Results                           | 31  |

| 5.2 Discussions                       | 32  |

|                                       |     |

| VI Conclusion                         | 52  |

| 6.1 Dissertation summary              | 52  |

| 6.2 Limitations and future work       | 52  |

|                                       |     |

| Riography                             | 61  |

# List of Tables

| Table | e                                                                            | Page |

|-------|------------------------------------------------------------------------------|------|

| 2.1   | The most common kernel functions                                             | . 14 |

| 4.1   | Parameters of the simulated cache                                            | . 25 |

| 4.2   | Benchmark application domain                                                 | . 26 |

| 4.3   | Benchmark combination                                                        | . 26 |

| 4.4   | The hit rate of the training data with different window sizes, approximately |      |

|       | first 100k accesses                                                          | . 27 |

| 4.5   | The number of data in bypass class in 100k training data                     | . 28 |

| 4.6   | SVM parameters                                                               | . 28 |

| 5.1   | Memory and cycles usage for each benchmark combinations                      | . 31 |

| 5.2   | Baseline LLC hit rate for each benchmark combinations                        | . 31 |

| 5.3   | Best hit rate achieved using 6 features and 7 features using training data   |      |

|       | with n=5000 window size $\dots$                                              | . 32 |

| 5.4   | Best hit rate achieved from the classifier prediction with 6 features and    |      |

|       | using training data with n=5000 window size                                  | . 32 |

| 5.5   | Best hit rate achieved from the classifier prediction with 7 features and    |      |

|       | using training data with n=5000 window size                                  | . 33 |

| 5.6   | The hit rate achieved from different kernel functions using 6 features and   |      |

|       | training data with n=5000 window size                                        | . 34 |

| 5.7   | The hit rate achieved from different kernel functions using 7 features and   |      |

|       | training data with n=5000 window size                                        | . 35 |

| 5.8   | Result of Com1 using 6 features from window size n=2000 training data        | . 37 |

| 5.9   | Result of Com1 using 6 features from window size n=5000 training data        | . 38 |

| 5.10  | Result of Com1 using 6 features from window size n=10000 training data $$    | . 38 |

| 5.11  | Result of Com1 using 7 features from window size n=5000 training data        | . 39 |

| 5.12  | Result of Com2 using 6 features from window size n=2000 training data        | . 39 |

| 5.13  | Result of Com2 using 6 features from window size n=5000 training data        | . 40 |

| 5.14  | Result of Com2 using 6 features from window size n=10000 training data $$    | . 40 |

| 5.15  | Result of Com2 using 7 features from window size n=5000 training data        | . 41 |

| 5.16  | Result of Com3 using 6 features from window size n=2000 training data        | . 41 |

| 5.17  | Result of Com3 using 6 features from window size n=5000 training data        | . 42 |

| Table | e                                                                                               | Page |

|-------|-------------------------------------------------------------------------------------------------|------|

| 5.18  | Result of Com3 using 6 features from window size n=10000 training data $$                       | . 42 |

| 5.19  | Result of Com3 using 7 features from window size n=5000 training data                           | . 43 |

| 5.20  | Result of Com4 using 6 features from window size n=2000 training data                           | . 43 |

| 5.21  | Result of Com4 using 6 features from window size n=5000 training data                           | . 44 |

| 5.22  | Result of Com4 using 6 features from window size n=10000 training data $$                       | . 44 |

| 5.23  | Result of Com4 using 7 features from window size n=5000 training data                           | . 45 |

| 5.24  | Result of Com5 using 6 features from window size n=2000 training data                           | . 45 |

| 5.25  | Result of Com5 using 6 features from window size n=5000 training data                           | . 46 |

| 5.26  | Result of Com5 using 6 features from window size n=10000 training data $$                       | . 46 |

| 5.27  | Result of Com5 using 7 features from window size n=5000 training data                           | . 47 |

| 5.28  | Result of Com6 using 6 features from window size n=2000 training data                           | . 47 |

| 5.29  | Result of Com6 using 6 features from window size n=5000 training data                           | . 48 |

| 5.30  | Result of Com6 using 6 features from window size n=10000 training data $$                       | . 48 |

| 5.31  | Result of Com6 using 7 features from window size n=5000 training data                           | . 49 |

| 5.32  | Result of Com7 using 6 features from window size n=2000 training data                           | . 49 |

| 5.33  | Result of Com7 using 6 features from window size n=5000 training data                           | . 50 |

| 5.34  | Result of Com7 using 6 features from window size n=10000 training data $% \left( 1\right) =0$ . | . 50 |

| 5.35  | Result of Com7 using 7 features from window size n=5000 training data                           | . 51 |

|       |                                                                                                 |      |

# List of Figures

| Figu | ire                                                                              | Page |

|------|----------------------------------------------------------------------------------|------|

| 1.1  | Percentage of distant reuse blocks in the 2MB LRU LLC over a memory-             |      |

|      | intensive benchmarks from SPEC CPU2006, $81.2\%$ of blocks are not reused        |      |

|      | before eviction and $25.6\%$ of blocks are never accessed again                  | 4    |

| 2.1  | Three types of cache organizations. This is an example of the cache where        |      |

|      | block address 13 can be allocated in the gray area. In direct-mapped, 13         |      |

|      | $\mod 8 = 5$ ; the block should be located at location 5. In two-set associative |      |

|      | cache, 13 mod $4 = 1$ ; the block can be allocated at one of the two blocks      |      |

|      | at location 1. In fully-associative cache, a block can be allocated anywhere.    | 8    |

| 2.2  | An example view of 32-bit address for 32-byte block. The block address           |      |

|      | is used to identify the block, the offset is used to identify which byte in      |      |

|      | the block. In case of n-way set associative, the tag is used for checking        |      |

|      | which block in the set, and the index is used to select which set. In fully      |      |

|      | associative the n in the index field is zero                                     | 9    |

| 2.3  | linear separating hyperplane for the separable case. The support vectors         |      |

|      | are circled. (Burges, 1998)                                                      | 13   |

| 3.1  | Organization of Jalminger and Stenström (2003) novel cache approach              | 21   |

| 3.2  | Organization of Piquet et al. (2007) bypassing method                            | 21   |

| 4.1  | An overview of the system                                                        | 24   |

| 4.2  | The marking method to create training data                                       | 27   |

| 4.3  | System Structure. The dotted arrows represent the information required           |      |

|      | by the classifier. The solid arrows represent data flows when cores request      |      |

|      | data from main memory (L2 missed)                                                | 29   |

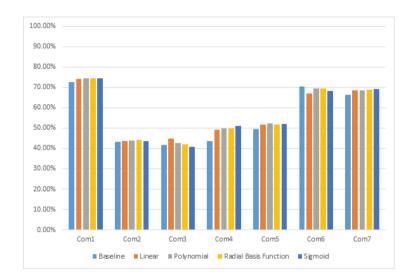

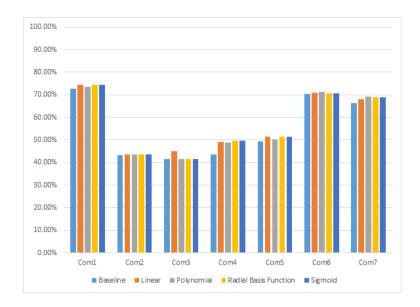

| 5.1  | Hit rate achieved from classifier prediction with 6 features and using train-    |      |

|      | ing data with n=5000 window size $\dots \dots \dots \dots \dots$                 | 33   |

| 5.2  | Hit rate achieved from classifier prediction with 7 features and using train-    |      |

|      | ing data with n=5000 window size $\dots$                                         | 34   |

| 5.3  | Best percentage improved compared with the ratio of the LLC accesses             |      |

|      | and the baseline hit rate (both scaled down for visualization)                   | 35   |

# CHAPTER I

# INTRODUCTION

Computer system performance nowadays relies heavily on the efficiency of the memory. Although the performance of the processor has drastically improved in the past decades, the access time to the main memory has sped up more slowly, therefore leaving a huge performance gap between processor and the memory, e.g., the processor performance is improving approximately 75% annum while the DRAM speed steadily increasing by 7% each year (McKee, 2004). In addition, there are efforts to increase the processor performance such as pipelining, branch prediction, out-of-order execution, which eventually leads to a memory bottleneck. The reason is that memory size is inversely proportional to memory performance, and size requirements increased more quickly than memory technology evolved. Main memory has improved, from SDRAM technology to DRAM and then to DDR-RAM technologies, which allows higher frequencies and bandwidths (HPm, 2010). However, these improvements still can not cope with the bandwidth required by processors for high utilization, maintaining a performance gap between performance and memory.

The concept of memory hierarchy is introduced to ameliorate the problem. The use of a small but fast associative memory called look-aside memory is suggested by Lee in 1963 to improve the overall performance of the computer. The term cache was first applied when it was implemented in the IBM System/360 Model 85 as a buffer between processor and main storage (Liptay, 1968). It was announced as a successful memory hierarchy implementation that reduced waiting time from storage from microseconds to nanoseconds. The aim of having the cache is to reduced the long waiting time to acquire data from the main memory. As the processor-memory performance gap increased, more levels of cache were used. The level closest to the processor is called the highest level or the level 1 cache (L1). The levels below are closer to the main memory and called L2, L3,..., last-level cache. For example, the Intel Pentium processor has level 1 on-chip cache and level 2 off-chip cache implemented (Horton, 1995); the L2 cache moved up to be on-chip in the Intel Pentium Pro (Pen, 1996). With the advent of multicore processors, several private and shared levels of cache are used, i.e., the Intel Core Xeon X5550 has four cores and three layers of cache: each core has private L1 and L2 cache; the Last-

level cache (LLC) is shared among four cores. With 2.66GHz processor speed, the size of the cache are 32KB and 256KB for L1 and L2 cache on each core, and the last-level cache size is 8MB. The access time to L1, L2, and L3, is approximately 4, 10 and 40 cycles, respectively, while the access time to the main memory is approximately 60ns or 120cycles (Levinthal, 2010). Sharing the LLC can reduce the number of duplicate copies when many cores are running identical applications. Also, when each core has different working set sizes, shared LLC has better utilization than private LLC. Throughout this dissertation, the term last-level cache and LLC will be used interchangeably.

An implementation of multilevel cache requires a definition of the relationship between each level. *Inclusion* defines a relationship in which data have copies in every lower levels of cache. When a datum is propagated from main memory to cache, a copy of it is allocated to all levels of cache. When a datum is modified, all copies of the data also have to be modified transparently. This is done to simplify the cache management and make the higher level cache work like an optimized lookup for the lower level cache. Whenever the upper level cache is full, the data block can be easily discarded because there is always another copy on the lower level cache; but if the datum on the lower level is discarded, all the other copies on the higher levels have to be discarded too. Also, since the last-level cache contains all the data from all upper levels, the looking up can be done by looking in the LLC only; this allows the L1 to work continuously without being disturbed. On the other hand, exclusion means that the data can have only one copy in all levels of cache, avoiding data duplicates. To allocate data on cache, all levels have to be checked to make sure that no other copies exist elsewhere. It reduces the space wasted from duplication but looking up a datum requires probing all levels of cache and managing zero duplication in all levels in all cores can be very complicated. The combination of the two is called non-inclusion, which does not force either inclusion or exclusion on cache. A datum can have multiple copies like an inclusive cache but when a datum is discarded from the lower level cache, the copies in the upper levels are not required to be discarded too. When the datum moves up from lower level to higher level, the exclusive cache will force deletion of the copy in lower level while the non-inclusive cache will allow leaving the copy in lower level, avoid wasting any blocks. In this dissertation, we focus on the non-inclusive cache only. Non-inclusive memory hierarchies are the simplest to implement, since each cache can manage its data independently of upper and lower levels. Although this complicates cache coherency mechanisms, it has been proven that non-inclusive cache achieve better performance than inclusive cache (Zahran, 2007). The extensive detail on the advantage of non-inclusive cache can be found in Zahran (2007).

Cache is efficient because it holds the data that are being used by the processors. The key idea that makes cache useful is the concept of locality of reference (Denning, 1972). The locality of reference is based on the notion that the memory access tends to be localized in time and space. It stems from the behavior of the programmers that tend to use data sequentially and looping. The tendency that next required data would be at the address adjacent to the currently used data means spatial locality while the tendency that same data will be used again soon means temporal locality. As the complexity of the programs increased, the memory-access behavior becomes more complicated and could exhibit larger access patterns. Algorithmic locality defines the access pattern that repeated, either in time or space, but in a manner larger than normal spatial or temporal locality. It would depend on the algorithm being used in the application. For instance, a computer simulation that repeatedly accesses a very large data set stored in dynamic data structures. The pattern could be captured by observing program behavior and adapting to it via run-time mechanism. With the benefit of localities, we can exploit the predictability and improve the memory system performance by accurately predicting which data should be allocated in cache and reduce the number of processor stall cycles.

Cache terms used to describe the efficiency of the cache are *cache hit*, which is when the processor requested data is found in cache, and *cache miss*, when the data is not found. The *hit rate* is the number of hits to the number of data accesses while the *miss rate* is the ratio of misses instead. Data in the cache are usually stored in *blocks* or *lines* whose sizes differ between architectures. The goal of using the memory hierarchy is to have a memory system that hides latency as much as possible, i.e., maximizes the hit rate and minimizes the access time, while maintaining the system cost-effective. The goal could be achieved by improving performance of cache by finding algorithms that accurately predict what to put in cache and how to replace it when it is full. For this reason, most researchers are focusing their works on techniques for bringing data to the cache which will be required in the near future, through some form of prediction (prefetching) and techniques for adequately managing which data to replace on cache when it is full (cache replacement policy).

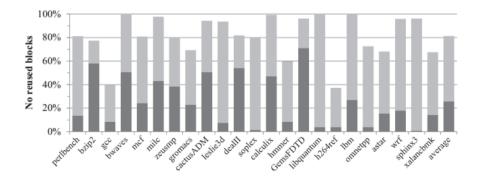

Nonetheless, with the use of multicore and multithreaded modern processors, memory usage has drastically changed to become more complex and the algorithms to manage cache need to be improved. In multicore, the last-level cache is usually shared and contention from many cores could cause memory thrashing, i.e., the working set is larger than the cache size and cause the requests to be constant misses. The complexity of the multicore workloads and the concern for energy consumption make writing all data to all levels of cache seem lavish. Many workloads today are multimedia applications which load millions of blocks of data and use them only once. Some data are placed in cache and never reused again until they are evicted from cache. This is especially true in the LLC, since exploitation of temporal locality in high level cache means an inversion of temporal locality on LLC; in other words, data that is accessed frequently will always hit on level 1 caches, thus remain unused on levels 2 and 3. Although the data is sometimes requested again from LLC (since L1 is smaller, it might eventually be evicted while it is still in LLC), the time between first and subsequent requests does not justify its presence on the LLC if it replaces more valuable data; hence, the justification for bypass. On levels closer to processor, the high temporal locality makes this approach less feasible. Study shows that numerous data blocks are allocated to the last-level cache and never reused or accessed again(Li et al., 2012). Fig 1.1 shows the percentage of distant reuse blocks in the 2MB LRU LLC over a memory-intensive benchmarks from SPEC CPU2006, 81.2% of blocks are not reused before eviction and 25.6% of blocks are never accessed again. Those blocks that are placed in the LLC and never accessed should never be allocated on cache to waste precious cache space. The method of not allocating some data to cache is called Cache Bypassing

Figure 1.1: Percentage of distant reuse blocks in the 2MB LRU LLC over a memory-intensive benchmarks from SPEC CPU2006, 81.2% of blocks are not reused before eviction and 25.6% of blocks are never accessed again.

Cache bypassing is a term describing a method that bypasses data from one or more levels of memory hierarchies. Bypassing could reduce costs from writing unnecessary data to cache and reduce memory bandwidth in transferring data. In fact, when the cache size is smaller than workload requirements, writing data to cache wastes more than the cost of writing only to memory. It also evicts existing valuable data from cache which could lead to more cache misses and increase processor stall cycles. For this reason, avoiding allocating never-accessed data is a good solution to improve cache performance. The use of the non-inclusive cache allows the data to be bypassed from the LLC without changing any existing architecture. Previous methods for classifying which data should be bypassed involved using predictors and counters. For example, applying the same approaches to bypass as the ones applied for branch prediction e.g., assuming a status until error and then reversing the status when it fails (Tyson et al., 1995; Jalminger and Stenström, 2003), or assuming one out of every n number should be bypassed (Kharbutli and Solihin, 2008; Kharbutli et al., 2013). This information was then stored on on-cache tables to direct bypassing logic. While these approaches sufficed for very simple workloads, these ad-hoc prediction methods can not be easily applied to complex, multicore workloads, driving the need for new bypass mechanisms. More sophisticated methods should be applied to the problem. Since we can simplify the problem into classification problem, data should be bypassed or not, it is known that the perfect method that could intelligently classify data into two groups is Machine Learning. The two-class classification is called binary classification; a field where Support Vector Machines have been known to excel. Hence, this dissertation explores the use of SVM for bypass prediction in shared Last Level Caches, in order to determine its suitability for the bypass problem.

## 1.1 Objectives of Research

- To develop an efficient cache architecture that allows bypassing based on the result of prediction.

- To develop a new technique to predict cache reusability based on machine learning algorithms.

# 1.2 Scopes of Study

The scope of this dissertation is limited to the following:

- This work would focus on improving cache performance in multicore processors, i.e. , quad-core or more using shared last level cache.

- The benchmarks that will be used to test the performance is SPLASH2.

- Performance measurement can be either instruction per cycle or the number of misses in accessing cache.

# 1.3 Summary of Contributions

In this dissertations, we provide the following contributions:

- We provide a proof of concept that machine learning is capable of predicting data reusability. It can decide whether to bypass data from cache.

- Support Vector Machine is an appropriate tool for classifying which data should be bypassed from the shared last-level cache.

- We provide a list of important attributes that have effects on making bypass decisions.

## 1.4 Dissertation Organization

The rest of the dissertation is organized as follows. The next chapter introduces background on cache and machine learning. Chapter 3 provides literature reviews in relevant fields. Chapter 4 describes the method to prove the theory we proposed. Then we show the results from the experiment in Chapter 5 and state the result discussions. Finally, the last chapter provides the summary of the dissertation, limitations, and future works.

# CHAPTER II

## **BACKGROUND**

In this chapter, we provide the background on cache and describe basic cache terms used in this dissertation.

### 2.1 Cache

Cache is the name given to the temporary storage that buffers between the processors and and the main memory. It can also mean any buffer that temporarily stores data to speed up the accesses to other storage devices. In this dissertation, we only focus on the cache that buffers data between the processors and the main memory. The goal of having a cache is to improve the performance of the processors by having data ready for the processors to use once needed, while maintaining the cost-efficiency balance. In general, the performance of the cache is defined by the following terms:

• Cache hit is a the ratio of the number of hits to the number of total cache accesses. Here, we represent them in percentage.

$$CacheHitPercentage = \frac{number of hits}{number of accesses} \times 100 \tag{2.1}$$

• Cache miss is the ratio of the number of misses to the number of total cache accesses. Here, we represent them in percentage.

$$CacheMissPercentage = \frac{number of misses}{number of accesses} \times 100 \tag{2.2}$$

• Latency is the amount of time that the processor has to wait for a datum, starting from request until reception of such datum.

To understand cache, further details on cache terminologies need to be mentioned.

### 2.1.1 Cache Organization

Cache stores data in blocks or lines whose sizes vary between architectures. In modern processors, the block size is usually 32-byte or 64-byte. Each block has an address

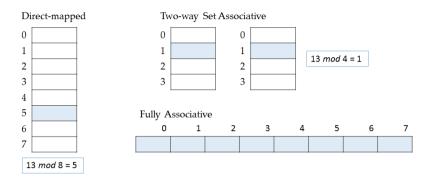

to identify itself. There are three basic organizations to arrange cache: fully associative, direct-mapped, and set associative. They are illustrated in Fig. 2.1

Figure 2.1: Three types of cache organizations. This is an example of the cache where block address 13 can be allocated in the gray area. In direct-mapped, 13 mod 8 = 5; the block should be located at location 5. In two-set associative cache,  $13 \mod 4 = 1$ ; the block can be allocated at one of the two blocks at location 1. In fully-associative cache, a block can be allocated anywhere.

In direct-mapped cache, a block can be allocated in one specific place. In general, the specific place is where the block address mod with the number of blocks in the cache. For example, if the address is 13 and the number of blocks in the cache is 8, the place to put the data is the block number 5. This makes the look up very fast for direct-mapped cache but it is possible that many data may require the same spot. The competition for the same block space is called *cache contention* and could degrade the performance. When it is fully associative cache, a block can be allocated anywhere in the cache so the cache contention for a block space does not occur. All the tags in all cache are looked up to find the match concurrently so it is very fast to find the requested data but the implementation requires more hardware cost to compare tags at all blocks at once. The combination of two organizations is a set-associative cache. It is when the blocks are grouped into sets, the block can be allocated where the block address mod with the number of sets in cache. For example, if the address is 13 and the number of sets is 4 and the size of each set is 2, the place to put the block can be one of the two blocks in set 1. The set-associative is a fast look-up time and cost-friendly organization. When there are n block in each set, the organization is called *n-way set associative*. A 32-bit address for a 32-byte block is shown in Fig. 2.2

| Block address |        | Offset           |

|---------------|--------|------------------|

| 28 bits       |        | 4 bits           |

| (28 – n) bits | n bits | 4 bits           |

| Tag           | Index  | byte in<br>block |

Figure 2.2: An example view of 32-bit address for 32-byte block. The block address is used to identify the block, the offset is used to identify which byte in the block. In case of n-way set associative, the tag is used for checking which block in the set, and the index is used to select which set. In fully associative the n in the index field is zero.

## 2.1.2 Cache Replacement Policy

Placing a data block on cache should be easy if the size of the cache is large enough to store all the data. In reality, the cache size is small to be efficient, fast and conserve energy. If the cache organization is direct-mapped, there is only one place to put the data block, no decision needs to be make as to where to allocate a new block into cache. However, when the cache is full and a miss occurs in the set-associative or fully-associative cache, the incoming block has to replace one of the data in cache. The block chosen to be replaced is referred to as a victim block. There are different methods to choose the victim block but a few basic cache replacement policies should be mentioned. Random replacement policy randomly selects the victim block to be replaced. The benefit is the simplicity in the implementation. In First In First Out (FIFO), the first block that goes into cache will be replaced first. It is also simple to implemented with simple hardware required. The most common policy is the least-recently used (LRU). All accesses to block have to be timely recorded and the block that has no reference (read or write) for the longest period is replaced first. Since the implementation of LRU is complicated and expensive, there is a simpler version of LRU called Pseudo-LRU which tries to approximate the LRU policy with less cost. The tree Pseudo-LRU is the most popular method widely used in modern processor caches. Its implementation is a binary search tree which recognizes which side of the leaf has been traversed. On a similar principle with LRU, the least frequently used (LFU) policy chooses the cache block that were referenced least often to be the victim block. With much less hardware overhead, not recently used (NRU) has one status bit to recognized if the block referenced recently. Besides from the basic cache replacement policies, Belady (1966) proposed a method to find the best performance possible from the cache replacement policy. The key idea is simply to find the block that will be reused furthest in the future to be a victim block. It requires knowledge of future accesses which

is impossible to implement but provides the best performance possible, typically as a baseline to compare with other methods. There are other recent replacement policies suggested by researchers to improve the cache performance; we will discuss them in the next chapter.

#### 2.1.3 Cache Writes

Most instructions read data and do not write to memory. However, there are two types of writes that need to be mentioned. When processors are writing to cache, the writing is to both cache and main memory. This policy is called Write through. When processors only write to cache and the modified cache block will be written to main memory later, it is called Write back policy. To identify which data is modified, there is a status bit attached to each cache block. The status bit is also called the dirty bit, its duty is to tell whether the data is modified. The write back has the advantage of saving the bandwidth between the cache and main memory. While the write through policy is easier to implement.

#### 2.1.4 Multilevel cache

In modern processors, the cache usually has one to three levels, namely, L1, L2, L3. The first level cache (L1) is the fastest cache but also smallest because of its price and the power dissipation. When there are many cores together, all levels of cache can be either private or shared cache. The term private means that the cache space belongs to one core and reads and writes are exclusive to that core only. On the other hand, shared cache means that any core can request to read and write the data on the cache. To use the limited space efficiently, L1 is commonly two split caches that separate instructions and data. The purpose is to allow the core to access both instruction and data simultaneously via two different ports. The second level cache (L2) is a larger, medium latency cache, mostly private to each core and implemented as unified cache, combining both instructions and data. The last-level cache (L3 or LLC) is normally unified cache which is shared among cores. The main benefit is more flexible and dynamic allocation of resources, for example, when some cores are idle, the active core can utilize the whole LLC space. Since shared last-level cache has become pervasive, there are many researchers focusing on improving the performance on this cache.

### 2.1.5 Cache Consistency

When many copies of the same datum exist, some policy must be employed to ensure that the processor receives the correct version of the datum requested. In case of writes, data in other places require transparent update to guarantee correctness. Cache coherence verifies that the data is updated in a timely fashion and memory consistency ensures that processors see exactly the same sequence of changes of all values. There are two cache coherence protocols used in modern processors, directory-based and snoopbased protocols. In directory-based protocol, the directory is a table storing state of each block such as ownership and its sharing status. It is scalable because directories can be distributed across memories. When there is a write to each block, the status in the directory has to be updated and send point-to-point updates to processors. On a snooping system, each cache monitors every bus, comparing the address with the ones it has stored. Should there be a match, the cache either updates its own copy or marks it as dirty. Although snooping is rather simple to implement in a small system, it does not scale well; in a many-core system with multiple caches, each would have to have access to every bus, leading to area and bandwidth issues. Thus, when the size of the cache is large, it is more popular to implement the directory-based protocol.

### 2.2 Machine Learning

Machine learning involves techniques and methods which give the machine an ability to learn from examples and provide patterns or predictions as results. It is designed to solve some tasks that could not be defined well by human or some complex problems which could not be solved by human. Each learning algorithm has different assumptions and creates different functions and is hence preferred for different kinds of problems, e.g., data mining, pattern recognition, classification, knowledge extraction, etc. They could be classified by types of learning to generate output function into two major groups, unsupervised learning and supervised learning.

Unsupervised learning refers to a method to uncover structure in unlabeled data. There is no reward or any signal that could evaluate the solution. Example problem that required unsupervised learning is data clustering, where objects are grouped into clusters based on similarities, e.g., document clustering which groups similar documents together. Another example is knowledge extraction in which we learn rules that are

underlined in data. In supervised learning, the input data are labeled with desired outputs as examples to be observed. An algorithm will try to generate a function that maps labeled input to desired outputs based on training data. The result function will be capable of distinguishing between different examples (or patterns) and predict answers for unseen data. If the desired output is discrete, the problem is called classification problem, and the function is known as a classifier. The classifier should accurately predict correct classes for any valid input data. In our problem, we could classify output as two groups of data, to be reused and never reused. This kind of problem is called binary or two-class classification where output could be generalized to simply answer with yes or no only. As it should be supervised learning, we need to label input data or patterns to give samples to the machine learning algorithms and selectively describe our input by features or the characteristic of data to solve our problem. This problem of binary classification could be solved by several machine learning methods, for example, decision tree, artificial neural network, support vector machines, etc.

Decision tree is a flowchart-like tree structure tool for supervised learning where internal nodes indicate a test on an input data, branches indicate the outcome of the test, and leaves or terminal nodes hold a class label. The process of testing starts at the topmost node or the root and repeats until the leaf node is reached and received the output. For its simplicity, decision tree is easy to understand and fast learning algorithm. It is used in large and realistic classification problems, such as medical diagnosis, credit risk analysis. However, decision tree is extremely sensitive to small perturbations in the data, i.e., a slight change can result in a drastically different tree, and our prediction is based on memory address of accessing data which could easily change over time and hence the tree needs to be reconstructed very often. Moreover, since our training data size needs to grow if the prediction accuracy is not good enough, training could be difficult because the tree needs to restart from the beginning if the training data has changed. Accordingly, the tree could not learn online and would not fit workloads that change continuously.

Support vector machine (SVM) is learning algorithm introduced by Cortes and Vapnik (1995), it is a prediction tool for classification and regression using machine learning theory to maximize predictive accuracy while avoiding over-fitting to data. In binary classification, its operation is to search for optimal hyperplane for linearly separable patterns by learning from sample data. SVM is used extensively in broad subjects to solve

different complex problems, e.g., web spam detection, facial recognition, medical data extraction, etc. Support vectors are the data points that lie closest to the decision surface where classification is most difficult. If the data is non-linearly separable, the kernel function will be applied to map sample data from original space to higher dimensional feature space to create a linearly separable pattern. The distance from the hyperplane to the instances closest to it on either side is called the *margin*. SVM will attempt to extend maximum margin between two class data samples while maintaining least errors.

Figure 2.3: linear separating hyperplane for the separable case. The support vectors are circled. (Burges, 1998)

To be specific, sample data are tagged with label -1 and +1 for the two classes. The training samples are  $\{\mathbf{x_i}, y_i\}$ , where  $i = \{1, .., l\}$  and  $y_i \in \{-1, 1\}$ ,  $\mathbf{x_i} \in R^d$ . The points  $\mathbf{x_i}$  which lie on the hyperplane satisfy  $\mathbf{w} \cdot \mathbf{x} + b = 0$ , where  $\mathbf{w}$  is normal to the hyperplane,  $\frac{|b|}{\|\mathbf{w}\|}$  is the perpendicular distance from the hyperplane to the origin, and  $\|\mathbf{w}\|$  is the Euclidean norm of  $\mathbf{w}$ . The equation could be written as

$$\mathbf{w} \cdot \mathbf{x_i} \ge +1 \text{ for } y_i = +1$$

$$\mathbf{w} \cdot \mathbf{x_i} \le -1 \text{ for } y_i = -1$$

which could be combine to

$$y_i(\mathbf{w} \cdot \mathbf{x_i} + b) \ge +1 \ \forall i \tag{2.3}$$

Any tuples  $\mathbf{x_i}$  that falls on the  $H1: \mathbf{w} \cdot \mathbf{x_i} + b = 1$  or  $H2: \mathbf{w} \cdot \mathbf{x_i} + b = -1$  hyperplanes are called support vectors and hence, the perpendicular distance from origin to the hyperplane H1 and H2 is  $\frac{|1-b|}{\|\mathbf{w}\|}$  and  $\frac{|-1-b|}{\|\mathbf{w}\|}$  respectively. Therefore the distance between two hyperplanes or the margin is  $\frac{2}{\|\mathbf{w}\|}$ . In order to predict patterns or classification of test data  $\mathbf{x^t}$ , the equation could re-written based on the Lagrangian formulation to find the maximum margin hyperplane as

$$d(\mathbf{x}^{\mathbf{t}}) = \sum_{i=1}^{l} y_i \alpha_i \mathbf{x}_i \mathbf{x}^{\mathbf{t}} + b_0$$

(2.4)

where  $y_i$  is the class label of support vector  $\mathbf{x_i}$ ,  $\mathbf{x^t}$  is a test tuple and  $\alpha_i$  and  $b_0$  are numeric parameters that were determined automatically by the optimization or SVM algorithm above; and l is the number of support vectors. We could test the tuple  $\mathbf{x^t}$  by plugging in equation 2.4 to see if the  $\mathbf{x^t}$  lie on which side of the hyperplane. Accordingly, if the result is positive, it means that  $\mathbf{x^t}$  lies on or above hyperplane H1 and it belongs to class +1. Otherwise, if the result is negative then  $\mathbf{x^t}$  lies on or below hyperplane H2 that it belongs to class -1. In case of non-linearly separable data, a kernel function could be used to maps the original data into a higher dimensional space. The most common kernel functions used are listed in Table 2.1

Table 2.1: The most common kernel functions

| Kernel                | Kernel Function                                                                           |

|-----------------------|-------------------------------------------------------------------------------------------|

| Linear                | $K(\mathbf{x}, \mathbf{y}) = \mathbf{x}^T \mathbf{y}$                                     |

| Polynomial            | $K(\mathbf{x}, \mathbf{y}) = (\mathbf{x}^T \mathbf{y} + 1)^q$                             |

| Radial Basis Function | $K(\mathbf{x}, \mathbf{y}) = exp\left[-\frac{\ \mathbf{x} - \mathbf{y}\ ^2}{2s^2}\right]$ |

| Sigmoid               | $K(\mathbf{x}, \mathbf{y}) = tanh(\delta \mathbf{x} \mathbf{y} - \delta)$                 |

## CHAPTER III

# LITERATURE REVIEWS

Many works have been focused on improving the performance of the cache. Various techniques can be divided into different groups; cache partitioning, cache replacement policy, cache prefetching, and cache bypassing.

## 3.1 Cache Partitioning

By exploiting benefits of locality, early works focus on improving the small directmapped cache by adding an extra buffer. To start with, Jouppi (1990) introduced an approach to improve the hit ratio of a direct-mapped cache by adding a small fullyassociative buffer called victim cache. The victim cache is used to hold the data evicted from the main cache and give them a second chance to be hit. It shows temporal locality of data that evicted data could be reused again. The improved hit rate of Jouppi's cache could be as good as two-way set associative cache but requires less circuitry. Similarly, a small buffer called assist cache is added to the main cache in HP-7200 (Hay et al., 1996) but it appears to function like a primary cache which stores incoming data and only forwards data that shows temporal locality to the main cache and bypass data that shows spatial locality back to the memory. Another work by Rivers and Davidson (1996) also add a fully-associative buffer called NT buffer to support the main cache. An NT bit is added to each line in caches to identify the non-temporal data and decide whether the data should be put in the NT buffer or the main cache. By managing data based on temporal locality, the cache is not polluted by non-temporal data so the conflicts in the main cache are reduced and the hit ratio is increased.

Adding identifying bits can help recognize lines that has temporal locality. Mc-Farling (1992) also uses sticky-bit and hit-last bit to note that the line has reused and should be kept in the cache. His dynamic exclusion gives priority to temporal data and preserved them in cache longer result in better cache performance. Difference approach in managing two different locality is proposed by González et al. (1995). González et al. proposed a cache that separated into two partitions based on data locality, temporal and spatial cache. When the predictor predicts that data has no locality, it will be bypassed from both caches.

## 3.2 Cache Replacement Policy

The main purpose of cache replacement policies is to predict which block in the cache should be the last one to be re-referenced and that last one should be replaced by a new block. As mentioned in Chapter 2, LRU is the basic cache replacement policy widely used in modern processors. LRU policy keeps track of the time when each blocks are being referenced (read or write). It is similar to a linked list that has the most recently used block, the latest block referenced, at the head of the list and the least recently used block at the tail. The victim block that will be replaced is always the one at the tail.

With LRU as basic replacement policy, some modifications to improve the LRU performance are proposed by changing the status of the block inserted, called the *insertion policy*. Qureshi et al. (2007) proposed LRU Insertion Policy (LIP) to insert the new incoming block at the end of the LRU chain instead. Unless promoted by being referenced again, the block will be replaced next. This gives priority to the block that is being rereferenced more than once. Another method proposed is Bimodol Insertion policy (BIP) which randomly selects where to insert the block, between the MRU and LRU, with more priority at the latter. The actual run, called Dynamic Insertion Policy (DIP), is implemented as set-dualing that switches between BIP and the traditional LRU policy depending on which policy is giving better hit rate at the time. A little modification of DIP is to make the algorithm thread aware. Thread-aware dynamic insertion policy (TADIP) has different counters for each different thread. The method claimed to achieve throughput near the traditional LRU with double cache size.

Besides from LRU, a number of researchers have proposed many methods to select the victim block. The challenge is to keep track of the time each block was referenced or to keep the list in order. The counter used to store the time or frequency could take up precious cache space. With the expense of implementing true LRU, Jaleel et al. (2010) proposed a Re-Reference Interval Prediction (RRIP) chain to replace the LRU chain by roughly dividing data into four groups. The RRIP represents the order that the blocks are predicted to be re-referenced from soonest to furthest. When cache is empty, the new incoming block is inserted in a position second from the furthest group. It will be promoted to the sooner group when it is referenced. When the cache is full, the block in the furthest group will be replaced first. The authors' method ensures that the data

repeatedly re-referenced stay longer in cache and the data that used only once (refer to as scan by author) are kept in the cache very shortly while requiring less hardware and outperforming traditional LRU policy. An improvement of the RRIP is proposed in Wu et al. (2011), Prefetch aware cache management (PACman) is a version of RRIP with the awareness of which blocks are prefetched or demand fetched. It gives the priority to the blocks that are demand-fetched to stay longer in the cache. As a result, PACman improved overall workloads more than 20% from traditional LRU replacement policy.

Khan et al. (2010) observed that the blocks in LLC are dead 86% of the time in memory-intensive benchmarks, i.e., the blocks are placed in cache and never reused again. To solve the problem, the authors create a predictor that samples program counter (PC) to determine if the block is dead and should be removed from LLC. The predictor can reduce the LLC miss rate from traditional LRU by 23% on multicore workloads while the sampling requires less overhead than conventional predictors with states storage.

## 3.3 Cache Prefetching

Prefetching is a method that moves a block of data up in the memory hierarchies before it is actually needed by the processor (Vanderwiel and Lilja, 2000). It could be done by either hardware or software or both. Software prefetch generally required sophisticated compilers to modify code in order to insert fetch data instructions. It would require extra processor cycles since it added extra lines to activate the prefetch in the code. As a result, it incurs in significant overhead and could degrade performance in some benchmarks as shown in Bernstein et al. (1995); Santhanam et al. (1997); Lipasti et al. (1995). Since software prefetch tends to specific within applications, we would focus on hardware prefetch here.

Hardware prefetch adds prefetching to the system with no need to modify the code. Smith (1982) notes in his survey that three important things to concern in prefetch are: 1) when the prefetch should be initiated 2) which data should be prefetched and 3) what status should be given to the prefetched data. First, the time to activate prefetch can be either prefetch-on-hit or prefetch-on-miss. Difference is prefetch activates when the data required by the processor is found in a cache or not. Sometimes it could be prefetch always, i.e., every time data in cache is accessed, but it would highly cost memory bandwidth. As the prefetched data displaces existing data in cache, if the prefetched data is fetched too

soon that it idles a long time in cache or it is removed before its use then that data will become *cache pollution*. Cache pollution could cause not only reduced cache performance but also wasted memory bandwidth and energy.

Second, choosing which data to prefetch is extremely important. Sequential prefetch exploits the spatial locality by prefetch data that adjacent to the currently accessed data. The simplest one is fetching one block of data that adjacent to the block currently accessed Smith (1978) called one block look-ahead (OBL). For example, if the address that is currently accessing is a then the prefetch data is a+1. The differences between current address a and the next address a+1 can be more than one and called *stride prefetching*. Jouppi (1990) introduced extra stream buffers to store prefetched next-address data separately from the main cache. Later, Baer and Chen (1991) record load/store instructions in the reference prediction table and predict future accesses that could be non-unit strides. It is called *stride prefetching*. Other works alternated stride prefetching by applied it to different memories Fu et al. (1992), Ibáñez et al. (1998), Kim and Veidenbaum (1997), Sklenar (1992).

Palacharla and Kessler (1994) proposed equal-sized stream buffers as a secondary cache. It detected strides and captures stream data behavior without the need for program counter which is very useful to memory other than on-chip cache. However, constant stride prefetching is only efficient on large programs with array or data accesses that exhibit spatial locality. For data access patterns that are different, Baer and Chen (1995) proposed aggressive prefetcher which predicts the size of stride dynamically. They also compare the method with Mowry et al. (1992) in Chen and Baer (1994) and concluded that the performance improvement depends on the program characteristics and there is no prefetcher with consistently better performance.

Other than stride-based prefetchers, Joseph and Grunwald (1997) interestingly apply Markov model to learn the miss addresses and predict addresses to prefetch. The Markov-like model is one kind of correlation-based prefetchers which use one address as a key and prefetch the next address follows that key. The disadvantage is that the prefetcher must see the miss reference repeats before it can predict future miss correctly. Sair et al. (2002) suggested that load instruction behavior can be classified into four groups as follow: next-stride, stride, same-object, and pointer-based, then concluded that the prefetch

should be able to classify the behavior and prefetch the correct stream of data. The same-object refers to prefetching a large object that loaded into different blocks. Zhang and Torrellas (1995) recognized if the objects are used together and prefetch all blocks. Pointer-based application is more difficult to predict since the addresses are not pattern. Many works (Collins et al., 2002; Cooksey et al., 2002; Ramos et al., 2000; Wang et al., 2003) are targeted to solve the problem. Sair et al. concluded that Markov predictor is suitable for the type. They improved and proposed predictor-directed stream buffer based on Sherwood et al. (2000) similar to Kandiraju and Sivasubramaniam (2002); Oly and Reed (2002) that also modified the Markov predictor and achieved impressive performance.

Besides from predicting method, there are software and hardware based lookahead method. Software means spending one thread to execute the program in advance only to fetch the correct prefetched data to another working thread Luk (2001); Moshovos et al. (2001); Roth et al. (1998). While hardware (Mutlu et al., 2003) use runahead technique to learn what to prefetch by allowing the processor to pretend to execute program during the processor stall cycles but not actually commit them. Similarly, Ganusov and Burtscher (2005); Zhou (2005), use advantages of multicore processor and let one core executes program ahead to prefetch correct data. These techniques are not quite popular because all the programs must execute twice only to reduce stall time, it would be a trade off between energy and time which may not worth spending.

For specific application like multimedia applications, Lee et al. (2003) examined data access patterns of multimedia applications and grouped them into three types, fixed-stride, 2way, and 2d streams and add three prefetchers to prefetch data to separated stream cache. As a result, the misses in multimedia benchmarks are drastically reduced. This work has showed that data access pattern in specific application could be learned and guided to achieve impressive performance. Somogyi et al. (2009) use the synergy between spatial and temporal locality to enhance prefetching performance. Their approach, Spatio-Temporal Memory Streaming (STeMS), looks at miss history to drive the prefetcher and prevent further misses through out the memory region.

#### 3.4 Cache Bypassing

The idea of predicting what data to fetch is similar to predicting which data not to cache. Tyson et al. (1995) proposed a method to manage data cache by selectively allow data allocation. It stems from observation that only small number of instructions are responsible for a large number of cache misses occurred in data cache, i.e., data allocation from some instructions are the main causes of cache misses. Consequently, those instructions should be prohibited from allocating data in cache in order to reduce the miss ratio. Instructions are marked with C/NA (Cacheable/Non Allocatable) if they are predicted to create a lot of misses. The prediction is made by a version of two-bit branch predictor by Yeh and Patt (1991). The important result is not the improved hit ratio but it is the substantially reduced memory bandwidth.

From the very first work, Johnson et al. (1999) proposed another cache bypassing which based the predictions on the memory access addresses instead of load instructions. They observed the memory access distribution and traversed through address trace to analyze the optimal bypassing decisions and the upper bound hit ratio that it could achieve. The prediction is predicted by partitioning data into Macroblocks and store access history in the Memory Access Table. It is reported that the result often achieved hit ratios close to the upper bound which is quite impressive improvement.

Later, Jalminger and Stenström (2003) applied the two-level branch predictor similar to Tyson's but the prediction is based on the memory access addresses like Johnson's. The aim is to predict whether a cache block will be reused within a limit distance or not. If the data will be reused then it would be allocated in the cache otherwise it would be placed in the bypass buffer for a short period. There are two types of table, one is for record each cache line access history called Reuse History Table and the other is for the two-bit predictor for each pattern per each cache line called Reuse Prediction Table. The two-bit predictor has four states which update every time a block is accessed based on the reuse history. Though Jalminger and Stenström's propose achieve high prediction accuracy (66%-94%) and reduce miss rate for up to 32%, it require a large amount of memory to record these tables and enormous bandwidth to update two tables every time the cache is accessed.

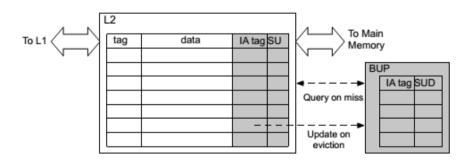

Piquet et al. (2007) observed that some data blocks are bought into cache and never

Figure 3.1: Organization of Jalminger and Stenström (2003) novel cache approach

accessed again before being evicted. Those blocks are named single-usage blocks (SU) and storing single-usage blocks on the cache creates single-usage pollution. The experiment shows that single usage pollution occurs only 6% of the time in L1 data cache but 33% in the L2 (last-level cache), and hence, data should be bypassed from the L2. The authors propose a method to decide which data should be bypassed based on the instruction who requested the data. Each line in the L2 is tagged with the Instruction Address (IA) and an SU bit that set to one when the data is accessed after being allocated in cache. The IA are stored in the BUP table accompanied with a counter. When a block in the L2 is evicted, the counter associated with the IA is updated; if the SU bit is one the counter is reset to zero, and if the SU bit is zero then the counter is incremented. When there is an L2 allocation, the IA is looked up in the BUP table. If the counter associated with the IA tag is saturated, the data block will be bypassed from the L2. The organization is shown in Fig 3.2

Figure 3.2: Organization of Piquet et al. (2007) bypassing method.

Another bypassing approach called Counter-based replacement and bypassing algorithm is introduced in Kharbutli and Solihin (2008). Kharbutli and Solihin observed that data that are brought to L2 cache often idle for a long period in cache after its last use because of the Least Recently Used (LRU) replacement policy that hold data a

long time before evicted. For some lines, they are never re-accessed again after they are brought to L2 cache. Therefore, the authors relaxed cache inclusion between L1 and L2 and suggested a method that detect never-reaccessed lines, bypass those lines from L2 cache, and load them to L1 only. Based on counter that count specific access to memory address, the authors proposed method to identify expired lines and replace them, also, it could identify bursty temporal data and put them in L1 cache only. As a result, the algorithm gain speed up in 10 out of 21 SPEC2000 benchmarks while degraded less than one percent in the rest.

Furthermore, Xiang et al. (2009) suggest that if the working set is larger than the cache size, remove only lines that will never reused at all is not enough to preserve the temporal data, more blocks should also bypass from cache. In addition, those blocks that will be reused only a few times should be removed by using Less Reused Filter (LRF). LRF consists of Reuse Frequency Predictor for predicting how many times each block will be reused, A filter buffer for storing less reused lines separated from the main cache, and the shadow tags for storing only tags of the evicted cache lines from the filter buffer. With the reuse count prediction, LRF could determine when the data should be placed. When most of the working sets are retained in cache the higher hit rate can be achieved. An improvement to LRF is proposed by Qiao et al. (2011) by adjusting LRF to be shared cache in multicore processor. It received better IPC compared to the uniprocessor and reduced the cache miss rate. The disadvantage of both LRF is the expensive hardware cost from keeping many counter values in each cache line and the large size of shadow tags.

Feng et al. predict data reusability based on previous reuse information and create a new replacement policy in Feng et al. (2011). The method adaptively switches between two predictors, reuse information based replacement policy and typical LRU replacement policy. Similarly, PDP (Duong et al., 2012) use reuse prediction to protect potentially reuse blocks in cache from being replace, if all the blocks are protected then the incoming block is bypassed. Optimal Bypass Monitor (OBM) (Li et al., 2012) tried to implement the optimal replacement policy and adding bypassing feature by comparing whether the incoming or the victim block will be reuse first and keep the nearest reuse data. The algorithm keeps track of the reuse information in the form of *incoming block* and *victim block* pair, and also requires another table to store a counter use to predict the reuse

distance of each incoming block. Storing and updating the two tables on every access cause enormous traffic amount. Another simple approach that claims to be more efficient than OBM is SCIP (Kharbutli et al., 2013). SCIP basically counts the number of time each block requested to L2. If the two-bit counter incremented to three then the LLC would allocate the block, bypasses around 75% of the data. As in their result, SCIP bypasses at least 82% of the incoming block and achieve an average of 18% speed up proving that the LLC require to allocate only some portion of data.

Combining partitioning and bypass, most recent work (Khan et al., 2014) proposed a cache management method that distinguishes between read and write requests and gives more priority to the read to reduce stalls from write. The author adapted the reuse prediction method in (Piquet et al., 2007) but only to predict data that will be read reuse only and bypass predicted writes and not reuse data from cache. The method speedup an overall average on SPEC2006 benchmarks 5% and 14% on caches-sensitive benchmarks compare to baseline LRU replacement policy.

# CHAPTER IV

# **METHODOLOGY**

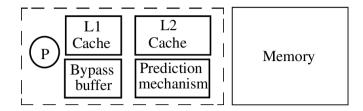

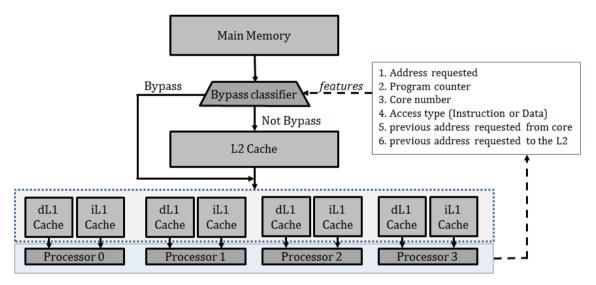

Shared cache behavior on multicore cannot be predicted by analyzing each core's workloads separately. The dynamics of multicore operation result in shared LLC effects, e.g., cache thrashing, that must be analyzed at shared LLC level. This is in contrast with private caches behavior where traces can be obtained directly from processor cores, and bypass algorithm could be directly deduced from processors behavior, e.g., by analyzing the program counter; this approach is not feasible for shared last-level caches where multicore interactions must be tackled by more sophisticated methods based on LLC access traces. In this chapter, we provide details on how support vector machine can learn from training examples and generate model classifier to predict which data should be bypass from the shared last-level cache. An overview of the system is shown in Fig. 4.1.

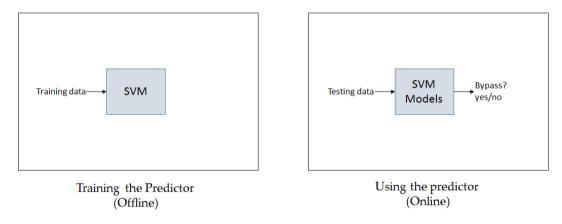

Figure 4.1: An overview of the system

The system is separated into two parts, the offline process and the online process. The offline process is the SVM learning process to generate models to classify data into bypass and not-bypass. It starts from deciding what are the data, getting those data from the simulator, and preparing the training data for the SVM. The online process is the cache simulation with the use of the bypass classifier to decide whether to allocate data on the last-level cache. The offline process detail will be described first and the online process detail will be described in the latter section.

## 4.1 The offline process

## 4.1.1 Preparing data

First, SVM requires labeled training data to learn. The definition of the training data is a set of known inputs with a known response to the input data. What we consider that should be the inputs of the SVM are the state of the parameters involving the memory and the core. The output is the class of the data, bypass or not-bypass. To create input data, we create a trace of addresses that the cores requested to use, both instruction and data, including all the features with the following motivations: 1) previous works (Piquet et al., 2007), (Khan et al., 2014) show that it is important to know which instruction is requesting the data, thus Program Counter (PC) has impact on making bypass decisions. 2) The locality of data provides the assumption that the data requested are related to the data previously requested, either in space or time. Therefore, the address of the previously requested data from the core and the previous miss from the higher level cache (L1) should have impact on bypass decision. 3) The core number that requested data indicates whose request generated from. It can help distinguish which application that is running and decide which application should be bypassed. 4) It is likely that data should be bypassed than instructions, so it is important to distinguish between the data and the instructions. 5) The temporal locality suggested that the time of access should be the key feature to decide bypassing. In conclusion, the trace includes the following information: address requested, program counter, core number that requested data, access type (Instruction or Data), previous address requested from the core, previous address requested to the LLC, and the time of access.

#### 4.1.2 The simulator

We use Multi2Sim simulator (Ubal et al., 2012) to model a quad-core processor with X86 ISA. All caches are non-inclusive, write-through and write-allocate with true LRU replacement policy. The cache parameters are depicted in Table 4.1.

Table 4.1: Parameters of the simulated cache

| L1 Instruction Cache       | 8KB, 32B-line size, 2-way  |

|----------------------------|----------------------------|

| L1 Data Cache              | 8KB, 32B-line size, 2-way  |

| L2 Shared Last-level Cache | 64KB, 32B-line size, 4-way |

Cache size is small in relation to benchmark memory usage (working set) in order to force contention in the shared last-level cache. Since the purpose is to prove the SVM ability to selectively bypass the data, two-level cache is sufficient to demonstrate the feasibility and exploiting the relationship between each core's private cache and the shared LLC.

#### 4.1.3 Benchmarks

We use SPLASH2 benchmarks because of its multithreaded support and its purpose of studying parallel machine. The application domain of each benchmark are summarized in Table 4.2. We create 7 benchmark combinations by randomly selecting 4 out of 11 SPLASH2 benchmarks to run simultaneously, four threads per benchmark. Each combination is listed in Table 4.3 and simulated for 200 million committed instructions after fast forwarding the first 100 million instructions.

Table 4.2: Benchmark application domain

| Program        | Application Domain         |

|----------------|----------------------------|

| Barnes         | High-Performance Computing |

| Cholesky       | High-Performance Computing |

| FFT            | Signal Processing          |

| FMM            | High-Performance Computing |

| LU             | High-Performance Computing |

| Ocean          | High-Performance Computing |

| Radiosity      | Graphics                   |

| Radix          | General                    |

| Raytrace       | Graphics                   |

| Water-nsquared | High-Performance Computing |

| Water-spatial  | High-Performance Computing |

Table 4.3: Benchmark combination

| com 1 | Raytrace, Radiosity, Water-nsquared, Water-spatial |

|-------|----------------------------------------------------|

| com 2 | Radiosity, Lu, Ocean, FFT                          |

| com 3 | Cholesky, Fmm, Water-nsquared, Radix               |

| com 4 | Barnes, Fmm, FFT, Radix                            |

| com 5 | Ocean, Lu, Barnes, Water-spatial                   |

| com 6 | Fmm, Cholesky, Lu, Raytrace                        |

| com 7 | FFT, Barnes, Radiosity, Water-nsquared             |

### 4.1.4 The training data

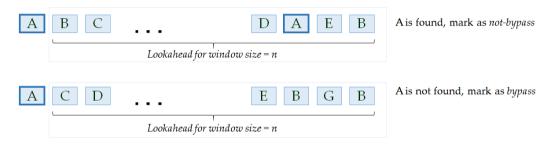

The traces are separated into two parts, the training set and the testing set. We select the first 1 million accesses to be the training data or the input for the SVM. The rest are reserved for testing the classifier generated by the SVM. On the training data, each datum must be identified, as belonging to "bypass" or "not-bypass" classes; the data is marked so it can be used for SVM training (sample data). We manually divide the data using our knowledge of future behavior, similar to the optimal lookahead in Li et al. (2012). The difference is the lookahead is limited to the window of size n to check for future reuse. The marking method is illustrated in Fig. 4.2.

Figure 4.2: The marking method to create training data

For example, when address A is accessed, LLC trace is checked for n addresses, determining whether or not address A will be reused. If so, then A will be marked as not-bypass and will be allocated in LLC normally. If not, then A is marked as bypass and will be bypassed from LLC. Experimental results suggest the most efficient window size for our experiment is n=5000; varying window size between 1000 and 10000. We show the result of our marking method with 3 different n sizes in Table 4.4.

Table 4.4: The hit rate of the training data with different window sizes, approximately first 100k accesses

| Name | Benchmarks                                         | baseline | n=2k  | n=5k  | n=10k |

|------|----------------------------------------------------|----------|-------|-------|-------|

| Com1 | Raytrace, Radiosity, Water-nsquared, Water-Spatial | 69.10    | 74.56 | 77.12 | 76.63 |