# SECURE BIT: BUFFER-OVERFLOW PROTECTION

By

Krerk Piromsopa

## A DISSERTATION

Submitted to

Michigan State University

In partial fulfillment of the requirements

For the degree of

DOCTOR OF PHILOSOPHY

Department of Computer Science and Engineering

2006

#### **ABSTRACT**

SECURE BIT: BUFFER-OVERFLOW PROTECTION

By

## Krerk Piromsopa

For decades, buffer-overflow attacks have remained the most persistent threat to the computer security world. The most common type of buffer-overflow attacks is an attack that changes the control flow by overflowing control data.

In this thesis, Secure Bit, architectural approach, is proposed to protect against bufferoverflow attacks on control data (return-address and function-pointer attacks in

particular). Secure Bit provides a hardware bit to enforce the integrity of addresses from

being modified by external data (input). Secure Bit is completely transparent to user

software; providing full backward compatibility with legacy user code. It can detect and

prevent all address-corrupting buffer-overflow attacks with little run-time performance

penalty. Addresses passed in buffers between processes are marked insecure and control

instructions using those addresses as targets will raise an exception. An important

differentiating aspect of this protocol is that once an address has been marked as insecure

there is no instruction to remark it as secure.

To validate Secure Bit, we first theoretically pursue a secure system with respect to buffer-overflow attacks and prove that Secure Bit provides a sufficient condition for preventing buffer-overflow attacks. Robustness and transparency are demonstrated by emulating the hardware, and booting Linux on the emulator, running application software

on that Linux, and performing known attacks. In addition to the cost analysis and issues related to the success of Secure Bit, we also suggest possible attacks that may not be protected by Secure Bit.

In addition to the proposed Secure Bit, this thesis also provides a survey of current approaches against buffer-overflow attacks. Notably, approaches are conceptually grouped into three broad categories providing a platform for studying buffer-overflow protection schemes.

For dad, the foremost inspiration of my life

### **ACKNOWLEDGEMENTS**

I would like to express my gratitude to all who contributed to the completeness of this thesis. Royal Thai Government and Department of Computer Engineering, Chulalongkorn University, Thailand gave me the opportunity to pursue this Ph.D. in the first place. I thank to everybody at the Department of Computer Science and Engineering and Michigan State University for making East Lansing a home away from home for the past few years.

It is my honor to work with the great advisor Prof. Dr. Richard J. Enbody. He helped me with not only the research, but also with my writing. Without his principle of keeping things simple, this thesis is not possible. If I am to be a good professor, he is certainly my role model. I am deeply indebted to him.

I thank to the committee members: Dr. Anthony Wojcik, Dr. Pang-Ning Tan, and Dr. Michael Shanblatt. Their invaluable suggestions and comments helped me to improve this thesis in many ways.

Last but not least, I thank my parents, my brother, and my wife for supporting me through these years. They made my life worth living.

### **Preface**

This thesis is divided into ten main chapters: introduction, review, theory, fundamentals, design, implementation, possible attacks, evaluation, analysis and conclusion. Though each chapter is written to be self-contained, reading the whole document in order is recommended.

Chapter 1, the introduction, presents the background of memory management from a system point of view, and the basic concept of buffer overflow. Through the chapter, readers are expected to learn the importance of protection against buffer overflow attacks.

Chapter 2, the background, reviews several approaches currently used by programmers, and architects to defeat buffer overflow. We generally try to explain a concept and point out the strength and weakness of each approach. Indirectly, we conclude that buffer overflow still needs a better solution.

Chapter 3, the theory, is intended to theoretically pursue a secure system with respect to buffer-overflow attacks. We begin by defining buffer overflows in general. Later in this chapter, we establish a sufficient condition for preventing buffer-overflow attacks and prove that it will create a secure system with respect to buffer-overflow attacks.

Chapter 4, the fundamentals of Secure Bit, proposes Secure Bit. In this chapter, readers will learn the concept of Secure Bit as an architectural approach for preserving the integrity of an address against buffer-overflow attacks.

Chapter 5, the design, is the discussion of architectural issues critical to the implementation and deployment of Secure Bit. This chapter provides sufficient concepts for adapting Secure Bit to any existing architecture.

Chapter 6, the implementation, elaborates the implementation details of Secure Bit in the BOCHS emulator and the modification necessary to the Linux kernel. Through the chapter, readers are expected to learn the impact of Secure Bit to both the architecture and the systems level.

Chapter 7, the possible attacks, is the analysis of possible methods that may be used to circumvent the protection provided by Secure Bit. We will present other types of attacks that are not protected by Secure Bit and discuss the possible solutions.

Chapter 8, the evaluation, is the assessment of protection provided by Secure Bit.

Chapter 9, the analysis, provides cost analysis and issues related to success of Secure Bit.

Chapter 10, the conclusion, summarizes the thesis and provides possible researches and applications in applying Secure Bit.

Finally, we hope to see the success of this research as an architecture solution against buffer overflow.

# **TABLE OF CONTENTS**

| LIST OF TABLESX |                                        |      |

|-----------------|----------------------------------------|------|

| LIST (          | OF FIGURES                             | XIII |

| CHAP            | TER 1 INTRODUCTION                     | 1    |

| 1.1             | MEMORY MANAGEMENT OF PROCESSES         | 1    |

| 1.2             | BUFFER-OVERFLOW ATTACKS                | 2    |

| 1.3             | FUNDAMENTAL OF BUFFER-OVERFLOW ATTACKS | 2    |

| 1.4             | SAMPLE ATTACKS AND VARIATIONS          | 4    |

| 1.5             | Summary                                | 10   |

| CHAP            | TER 2 REVIEWS                          | 11   |

| 2.1             | Introduction                           | 11   |

| 2.2             | PROTECTION SCHEMES                     | 12   |

| 2.2             | 2.1 Static Analysis                    | 12   |

| 2.2             | 2.2 Dynamic Solutions                  | 13   |

| 2.2             | 2.3 Isolation                          | 16   |

| 2.2             | 2.4 Summary of Protection schemes      | 17   |

| 2.3             | STATIC ANALYSIS                        | 18   |

| 2.3             | 3.1 Lexical Analysis                   | 18   |

| 2.3             | 3.2 Semantic Analysis                  | 20   |

| 2.4             | DYNAMIC SOLUTIONS                      | 20   |

| 2.4             | 4.1 Address Protection                 | 20   |

| 2.4             | 4.2 Input Protection                   | 31   |

| 2.4             | 4.3 Bounds Checking                    | 34   |

| 2.4             | 1.4 Objuscation                        | 37   |

|    | 2.4.5       | Isolation                                   | <i>38</i> |

|----|-------------|---------------------------------------------|-----------|

| 2  | 2.5         | Analysis                                    | 41        |

|    | 2.5.1       | Pitfalls                                    | 41        |

|    | 2.5.2       | Performance                                 | 42        |

|    | 2.5.3       | Compatibility (Transparency)                | 42        |

|    | 2.5.4       | Deployment and Cost                         | 43        |

| 2  | 2.6         | CONCLUSIONS                                 | 44        |

| CH | IAPTI       | ER 3 BUFFER-OVERFLOW PROTECTION: THE THEORY | 45        |

| 3  | 3.1         | Buffer Overflow                             | 45        |

| 3  | 3.2         | Prevention                                  | 47        |

| 3  | 3.3         | SUMMARY                                     | 50        |

| CH | IAPTI       | ER 4 FUNDAMENTALS OF SECURE BIT             | 51        |

| ۷  | <b>4</b> .1 | GENERAL MECHANISMS                          | 51        |

| ۷  | 1.2         | FORMALIZATION OF CONCEPT                    | 53        |

| ۷  | 1.3         | PROTOCOL ENFORCEMENT                        | 55        |

| ۷  | 1.4         | SUMMARY                                     | 57        |

| CH | IAPTI       | ER 5 DESIGN                                 | 58        |

| 4  | 5.1         | MEMORY ARCHITECTURE                         | 58        |

|    | 5.1.1       | Memory Organization Modification            | 59        |

|    | 5.1.2       | Interleaving Memory                         | 60        |

|    | 5.1.3       | Secure Bit Relocation (Shared Memory)       | 61        |

| 4  | 5.2         | INSTRUCTION SET ARCHITECTURE                | 62        |

|    | 5.2.1       | Arithmetic and Logical Instructions         | 63        |

|    | 5.2.2       | Control Instructions                        | 64        |

| 5  | 5.3         | OPERATING SYSTEM                            | 65        |

|    | 5.3.1       | Domains and Buffer Manipulation             | 65        |

| 5.3  | .2 Virtual Memory                    | 66                                     |

|------|--------------------------------------|----------------------------------------|

| 5.4  | SUMMARY                              | 68                                     |

| CHAP | TER 6 IMPLEMENTATION                 | 69                                     |

| 6.1  | BOCHS EMULATOR                       | 69                                     |

| 6.2  | Memory                               | 70                                     |

| 6.2  | .1 Memory allocation                 | 70                                     |

| 6.2  | .2 Memory interface                  | 71                                     |

| 6.3  | Instruction Set Architecture         | 73                                     |

| 6.3  | .1 Operations                        | 74                                     |

| 6.3  | .2 Data Manipulation                 | 74                                     |

| 6.3  | .3 Control Data                      | 75                                     |

| 6.4  | Linux                                | 75                                     |

| 6.5  | Summary                              | 78                                     |

| СНАР | TER 7 POSSIBLE ATTACKS ON SECURE BIT | 79                                     |

| 7.1  | ATTACKS ON NON-CONTROL DATA          | 80                                     |

| 7.2  | FALSE POSITIVES                      | 83                                     |

| 7.3  | SUMMARY                              | 83                                     |

| CHAP | TER 8 EVALUATION                     | 85                                     |

| 8.1  | BOOTING LINUX                        | 85                                     |

| 8.2  | COMPATIBILITY                        | 86                                     |

| 8.3  | MOUNTING ATTACK                      | 89                                     |

| 8.4  | Instruction Set Architecture         | 93                                     |

| 8.5  | SUMMARY                              | 94                                     |

| СНАР | ΓER 9 ANALYSIS                       | 05                                     |

|      | TER 7 ANALISIS                       | ······································ |

| 9.2    | DEPLOYMENT                                    | 95       |

|--------|-----------------------------------------------|----------|

| 9.3    | SPACE                                         | 96       |

| 9.4    | PERFORMANCE                                   | 96       |

| 9.5    | POWER CONSUMPTION                             | 96       |

| 9.6    | COST ANALYSIS                                 | 97       |

| СНАРТ  | TER 10 CONCLUSION                             | 99       |

| 10.1   | CONTRIBUTIONS                                 | 99       |

| 10.2   | SECURE BIT                                    | 100      |

| 10.3   | FUTURE RESEARCH                               | 101      |

| 10.4   | Conclusion                                    | 101      |

| APPEN  | DIX A: SECURE BIT 1: THE ORIGIN               | 103      |

| APPEN  | DIX B: NON-LIFO CONTROL FLOW                  | 108      |

| APPEN  | DIX C: TCPA, INTEL LAGRANDE, AND MICROSOFT NO | GSCB 110 |

| BIBILO | OGRAPHY                                       | 114      |

# **LIST OF TABLES**

| Table 1 Directory structure of Linux Kernel | 76 |

|---------------------------------------------|----|

| Table 2 Results from stack smashing test    | 91 |

| Table 3 Results from GOT test               | 93 |

# **LIST OF FIGURES**

| Figure 1 Memory management model of a process                                                                                            | 1  |

|------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2 Stack Smashing                                                                                                                  | 5  |

| Figure 3 An example of a vulnerable program                                                                                              | 8  |

| Figure 4 Buffer-Overflow Attacks on Pointers                                                                                             | 9  |

| Figure 5 Algorithm of Static Analysis                                                                                                    | 12 |

| Figure 6 Algorithm of Dynamic Solutions                                                                                                  | 13 |

| Figure 7 Taxonomy of solutions against buffer-overflow attacks                                                                           | 17 |

| Figure 8 Sample of code reordered by IBM ProPolice                                                                                       | 22 |

| Figure 9 LibVerify. (From [2])                                                                                                           | 29 |

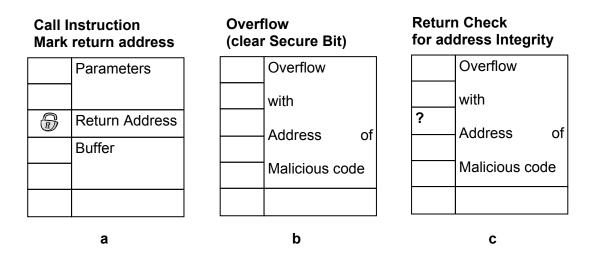

| Figure 10 Memory Snap shot with Secure Bit (a) normal operation. (b) Passi across domains. (c) Related instructions validate the address |    |

| Figure 11 State-transition diagram of buffer-overflow attacks                                                                            | 54 |

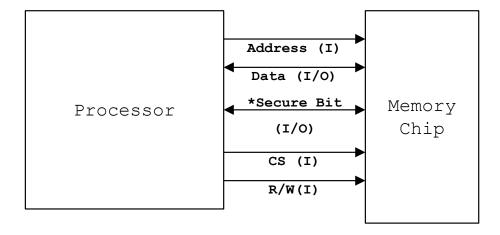

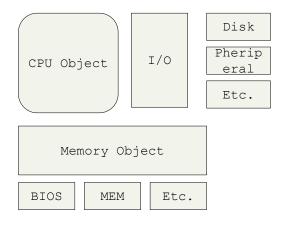

| Figure 12 System block diagram                                                                                                           | 58 |

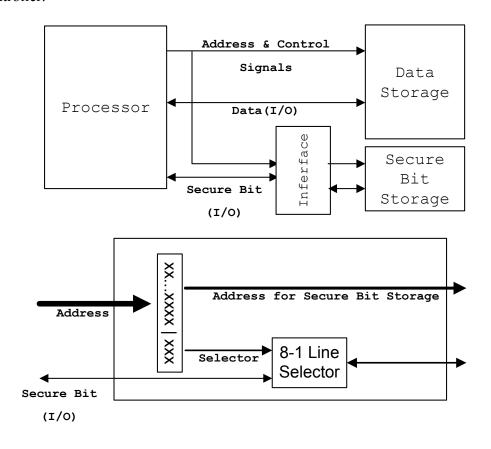

| Figure 13 Interleaving Memory Interface and Secure Bit controller                                                                        | 60 |

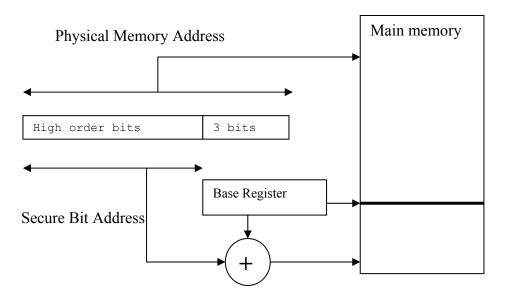

| Figure 14 Address translation scheme for Secure Bit Relocation                                                                           | 61 |

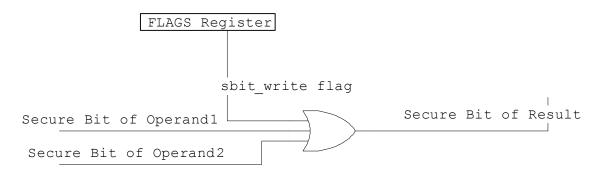

| Figure 15 Operations of Secure Bit                                                                                                       | 64 |

| Figure 16 BOCHS Components.                                                                                                              | 69 |

| Figure 17 Memory Allocation for storing Secure Bit                                                                                       | 70 |

| Figure 18 Code for (a) manipulating Secure Bit (b) reading Secure Bit                                                                    | 72 |

| Figure 19 List of overloading functions for accessing physical memory                                                                    | 73 |

| Figure 20 Macros for operations on Secure Bit                                                                                            | 74 |

| Figure 21 Data manipulation using sbit_write mode                                                                                        | 75 |

| Figure 22 Validation of Secure Bit in control instructions                                                                               | 75 |

| Figure 23 Linux Kernel Organization                                                                                 | 77           |

|---------------------------------------------------------------------------------------------------------------------|--------------|

| Figure 24 Macros for managing sbit_write mode (in "/include/asm-i386/ua                                             | ccess.h") 77 |

| Figure 25 Sample Buffer-Overflow attack on non-control data                                                         | 80           |

| Figure 26 Example of stack smashing venerability                                                                    | 90           |

| Figure 27 Wrapper program for exploding stack smashing                                                              | 91           |

| Figure 28 Example of GOT vulnerability                                                                              | 92           |

| Figure 29 Wrapper program for exploding GOT example                                                                 | 93           |

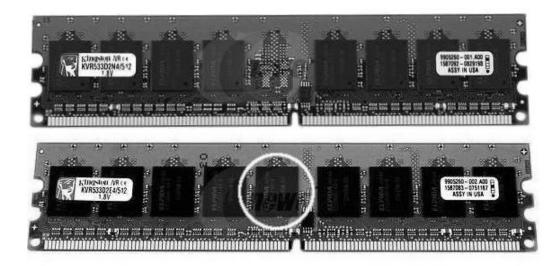

| Figure 30 Top: DRAM card without ECC; Bottom: DRAM card with an chip for ECC                                        | _            |

| Figure 31 Semantic of call and return function                                                                      | 105          |

| Figure 32 Stack snapshot with Secure Bit (a) After call instruction, (b overrun, and (c) During return instruction. |              |

| Figure 33 Function pointer protection using Secure Bit.                                                             | 106          |

| Figure 34 Sample IA-32 optimization of near call and far call for size                                              | 108          |

| Figure 35 Intel LaGrande Architecture (from [36])                                                                   | 111          |

# **Chapter 1** Introduction

This chapter is intended to be an introduction to buffer overflows. We begin by revisiting the memory management of processes in generic operating systems. Based on the memory management, we continue to explore buffer overflows in general, and returnaddress attacks and function-pointer attacks in particular. Included is an example of a multistage buffer-overflow attacks which can bypass most solutions.

# 1.1 Memory Management of Processes

Knowledge of how modern operating systems handle the memory of processes is required in order to understand how buffer overflows happen. From a programmer's point of view, the memory of each process is partitioned into text (code) and data. Similarly, the operating system partitions the memory into several sections (also referred to as segments). Apart from the text and the data, the operating system also allocates memory for the heap, the BSS, and the stack. This memory model is applied to both UNIX-like systems and WINDOWS systems. Figure 1 shows the model and growing direction of each segment.

| Stack | (growing down) |  |

|-------|----------------|--|

| Неар  | (growing up)   |  |

| BSS   |                |  |

| Data  |                |  |

| Text  |                |  |

Figure 1 Memory management model of a process

The text segment is the area where the program binary is stored. The data segment consists of all initialized global data and global variables. The BSS (Block Started by Symbol) is allocated for additional space determined at compile time. This space stores

static variables and all uninitialized global variables. Compilers are responsible for generating these three segments. The heap is the space that a program can dynamically allocate at execution time. The stack is typically used for storing local variables, arguments and return addresses. A snapshot of data stored in the stack is shown in Figure 1.

While the text segment can easily be protected by labeling as read only, the others cannot. Thus, it is possible for users to arbitrarily modify data in those areas. In the next section we learn a class of attack where input is used to maliciously modify control data and cause a program to be in unexpected state. This kind of attack is known as a "buffer-overflow attack".

## 1.2 Buffer-Overflow Attacks

We begin by establishing the fundamentals of buffer-overflow vulnerabilities and attacks.

Later we present variations on buffer-overflow attacks.

## 1.3 Fundamental of Buffer-Overflow Attacks

Several researchers ([12, 15, 23, 27, 38, 46]) have positioned that there are two necessary conditions for buffer-overflow attacks to be successful: (1) injecting malicious code and (2) redirecting the program control flow to execute that code. Although it is common, injecting malicious code is not necessary since the code can be resident code found in shared libraries. For example, jumping to resident shell code while in privileged mode is sufficient. Therefore, we claim that only the second condition is truly necessary.

We first take a quick look at buffer overflow vulnerabilities and how they were first exploited. A buffer overflow is an anomalous condition where a program somehow writes data beyond the allocated end of a buffer in memory [76, 81]. The eventual result is an access to unexpected data [56, 11]. A buffer-overflow attack is a buffer overflow that overwrites critical data and results in malicious or unexpected behavior. Examples range from denial of services to gaining privileged control over the target system [56, 11]. In all cases, the malicious data in an attack are input data, such as data from another domain (e.g., user inputs, network packets, data passed from another process), that was not verified. It is possible for buffer overflow to take place entirely within a process, but such a condition usually results in segmentation fault rather than an attack.

With this observation, we define a *buffer-overflow attack* to be

an attack caused by overflowing a buffer with data from another domain which results in malicious or unexpected behavior of a program.

This concept is not new. For example, Howard and LeBlanc state in their book "All input is evil until proven otherwise" [32] Accordingly, an intuitive solution against buffer-overflow attacks is an ability to detect and validate input, especially input which is eventually used for control.

Using the concept that inputs are the origin of attacks, a key component for detecting and validating the input is metadata. Metadata is additional information on the properties of data. It can be one or a combination of: type descriptor, guard value, encoding key, redundancy copy of data, tagged value, or even programming logic. This concept is also

not new. It was suggested that metadata is a key to preventing buffer-overflow attacks in the 2003 article [29]. In this chapter we will use the variety of metadata and its management as a way of classifying buffer-overflow prevention schemes.

Note that metadata can also be used for other purposes, e.g. tagged architectures such as Symbolics [47] or tagged operating systems [28]. However, the main focus of this thesis is on the use of metadata for buffer-overflow attack prevention.

In summary, buffer-overflow attacks occur when a malformed input is being used to overflow a buffer causing a malicious or unexpected result. Some metadata is necessary for prevention. In Chapter 2, we will present a variety of schemes for handling buffer-overflow attacks. Most of them use metadata.

# 1.4 Sample Attacks and Variations

There are two main targets of buffer-overflow attacks: control data and local variables. In the vast majority of attacks, control data is the target so prevention schemes have focused on control data. Control data can be divided into several types: return addresses, function pointers, and branch slots. Return addresses have been the primary target since their location can easily be guessed. More advanced buffer-overflow attacks target other control data. Some literature refers to attacks on return addresses as first-generation attacks, and those on function pointers as second-generation attacks [11].

The first step-by-step description of how to construct a buffer-overflow attack was written by Elias Levy (a.k.a. Aleph One) in 1996 [51]. In his paper, the term "Stack

Smashing" is probably first used to refer to the plastering of stack with shell code and its address to set up an eventual overflow of a return address on the stack.

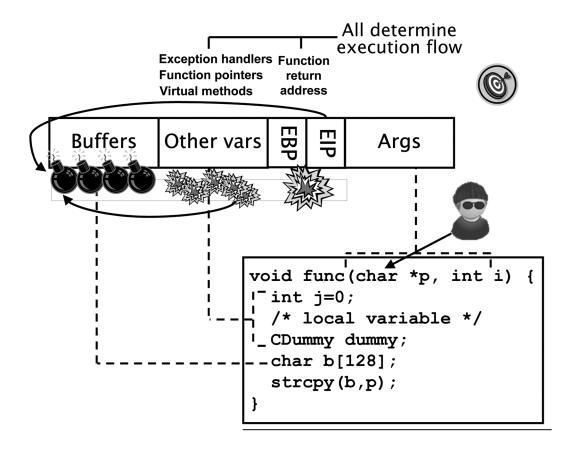

Figure 2 Stack Smashing

Figure 2 shows a stack-smashing example. In this example, attackers (shown in the black hat) will pass a buffer containing malicious code (e.g. shell) and multiple copies of the address of the target buffer as an argument to the vulnerable program (through parameter p). A buffer manipulation function (e.g. strcpy in this example) will overflow the function's return address with the address of the target buffer (which contains malicious code). The eventual result is that the return instruction will use the address of the target buffer as a return address and return the program flow to execute that malicious code. Additional attack vectors are provided but not used in the code such as function pointer fp.

As outlined above, it is important to note that the critical component of this attack is the modification of the return address (replaced by the address of the target buffer).

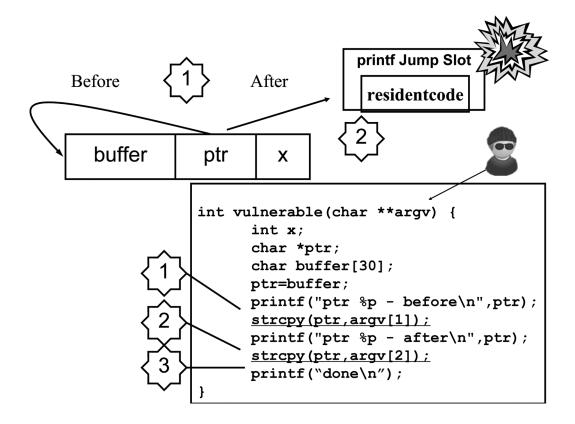

To illustrate an advanced buffer-overflow attack, we provide a multistage buffer-overflow attack (a.k.a. Hannibal Exploit [19]) that can bypass most software buffer-overflow solutions. Fundamental to a multistage buffer-overflow attack is that there exists a vulnerable pointer to a buffer. That is, there is a user-writeable buffer sufficiently near a useful pointer. First, the pointer is modified (by overflowing) to point to a specific location (e.g. a jump slot or a function pointer). In the second stage of the attack, an input is stored at the pointer's target. These two steps allow attackers to create a pointer to any location (first stage) and overwrite the pointer's target with a desired value (second stage). The next time some program jumps to that target, it will be redirected based on the value inserted by the attacker. In particular the program will be redirected to the attacker's malicious code. For example, if the program is running in privileged mode and the pointer points to shell code, the attacker will have created a privileged shell allowing free reign. Figure 3 is an example of such a vulnerable program.

Before examining the code, let's review how a jump table is used. Consider the slot in the table for the pointer to the *printf* executable. A call to *printf* indexes to that slot in the table and then jumps to the *printf* executable.

To attack this type of program, the buffer-overflow is done in two stages. First, the *ptr* pointer is overflowed to point to a desired memory location (1), e.g. the *printf* slot in the

jump table. In particular, argv[1] controlled by the attacker will contain the address of the *printf* slot in the jump table. The strepy routine will copy argv[1] into *buffer*, but overflows to overwrite ptr with the printf address slot. In the figure, we see that the pointer ptr originally pointed to 'buffer' (arc labeled 'Before') but now points to the jump slot (arc labeled 'After). Now that ptr points to the printf slot in the jump table, we need to insert a desired value into that slot.

Suppose, for illustration, that we also have determined the address of resident shell code (we will call it residentcode). Using our modified ptr we will overwrite the jump table slot with the residentcode address. We use the second strcpy call (2) to write argv[2] (also controlled by the attacker and whose value is residentcode) into the target of ptr which now points to the *printf* entry in the jump table. The result of that second strepy call is that we have placed the address residentcode (resident shell code) into the printf slot of the jump table. The attacker has achieved his goal. Now when a program calls printf, control passes as usual to the printf entry in the jump table, but now the attacker has redirected control to residentcode, the address of the shell code. Instead of printf a shell will be started. If the program which called *printf* was operating in privileged mode, the attacker will have succeeded in creating a privileged shell with full system access. (See [57] for more details). As we will see below, this multi-stage attack gets around most buffer-overflow protection schemes. Less obvious is that we can use a similar approach to circumvent some software solutions to buffer-overflow attacks by modifying a handling vector which can allow us to bypass the buffer-overflow handling routine.

Figure 3 An example of a vulnerable program

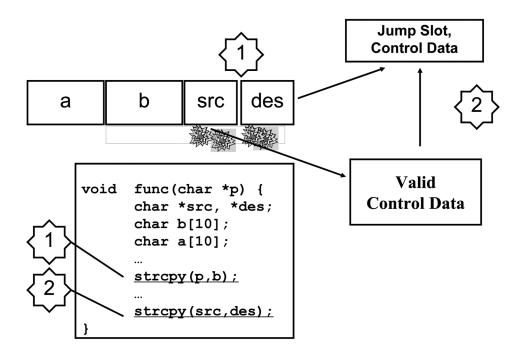

Another variation which most schemes cannot protect is an attack on generic pointers. By modifying both the source and destination pointers, copying from one arbitrary memory location to another is possible. Figure 4 illustrates an attack based on attacking pointers. In this figure, the first *strcpy* will allow attackers to overflow buffer *b* so the *src* and *des* pointers are replaced with two pointers of the attacker's choice: in this case, valid control data and target address respectively. The second *strcpy* will then copy from the *src* location to the *des* location. Using this approach, it is possible to modify any memory entry with a known local entry while avoiding most protection mechanisms. For example, an encoded function pointer can be used to attack another function pointer (e.g. jump slot).

Figure 4 Buffer-Overflow Attacks on Pointers

A related attack is worth noting here: printf vulnerabilities [63]. Malformed formatting instructions can allow arbitrary memory to be overwritten. It is not a buffer-overflow attack, but with the ability to overwrite arbitrary memory the attack then proceeds like many buffer-overflow attacks by attacking control data. Some buffer-overflow schemes can prevent some of those attacks. However, any variable can also be attacked, and no buffer-overflow scheme protects arbitrary data. Fortunately, simple static analysis of source code can identify printf vulnerabilities. As we will see below, static analysis is not sufficient for buffer overflows.

Recently "integer overflows" (known more generically as "integer arithmetic" attacks) have emerged as a variation [5]. In these attacks guard data which protects buffers is attacked. After defeating the guard data some buffer-overflow attack is used. Therefore,

these attacks can be considered as a variation of a buffer-overflow attack which the more robust schemes can protect against.

An attack on local variables is exemplified by the classic password attack from 1987 paper [80]. Basically, a variable is being overflowed allowing an arbitrary password to be validated resulting in root or administrator access. No control data is involved so no existing buffer-overflow protection schemes protect against this type of attack.

# 1.5 Summary

Through the chapter, we have learned the fundamentals of buffer-overflow attacks that can occur in any user accessible area. In the big picture, a buffer-overflow attack is the effect of modifying critical data by overflowing a buffer. The critical data are control data and generic variables. Most attacks target control data. When control data is the target, attackers are then able to redirect the control flow to execute the unexpected code.

# Chapter 2 Reviews

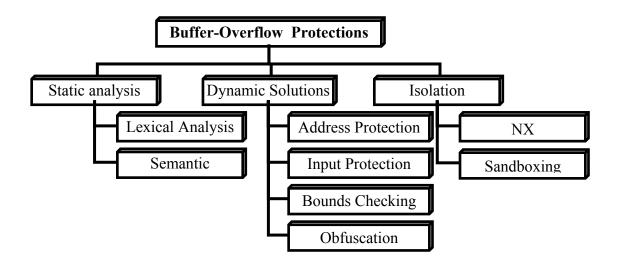

This chapter is the review of current approaches against buffer-overflow attacks. To elucidate the wide variety of approaches, the methods are categorized to form a taxonomy (in Figure 7). For each class in the taxonomy, we briefly discuss the mechanisms and the (potential) problems.

### 2.1 Introduction

Although they date back to the infamous MORRIS worm of 1988 [62], buffer-overflow attacks remain the most common type of attacks. Though skilled programmers should write code without buffer overflows, no program is guaranteed free from bugs so it cannot be considered completely secure against buffer-overflow attacks. The persistence of buffer-overflow vulnerabilities speaks to the difficulty of eliminating them. In addition, as buffer overflow vulnerabilities are eliminated in operating systems, they are being found and exploited in applications. When applications are run with root or administrator privileges, the impact of a buffer overflow is equally devastating.

In an effort to avoid relying on individual programming skill, a number of researchers have proposed a variety of methods to protect systems from buffer-overflow attacks. Most of them are not able to provide complete protection. For example, some only prevent the original stack-smashing attack, but can be circumvented by more recent attacks.

### 2.2 Protection schemes

In Chapter 1, we have established a basis for understanding buffer-overflow attacks so we can now examine current approaches to protect against them. We partition the approaches into three broad categories: static analysis, dynamic solutions, and isolation. Static analysis tries to fix functions that are vulnerable to buffer-overflow attacks. Dynamic approaches monitor or protect data that is either a target or the source of buffer-overflow attacks. Isolation seeks to limit the damage of attacks.

## 2.2.1 Static Analysis

Given a set of known vulnerabilities, we can simply avoid buffer-overflow attacks by fixing the vulnerable functions. Since this approach works on source code it is called "Static Analysis."

The main idea of "Static analysis" is to find and solve the problem before deploying the program. To do so, we first analyze the source code or disassembly of the program by looking for code with a predefined signature. For example, it is well known that the "strcpy" function in C can be vulnerable to buffer-overflow attacks. Knowing this fact, we can create a signature to search for any use of the "strcpy" function, warn the programmer of the vulnerability and suggest solutions (e.g. using the bound-checking version "strncpy"). A generic static analysis algorithm is presented in Figure 5.

Figure 5 Algorithm of Static Analysis

## 2.2.2 Dynamic Solutions

Knowing which data are critical to attacks, we can prevent attacks by validating the integrity of that data. As mentioned above, the data of interest are control data such as (but not limited to) return addresses. We name these "Dynamic Solutions" because data are dynamically managed and verified in the run-time environment. The generic algorithm is shown in Figure 6.

```

// Dynamic Buffer-Overflow Protection

// During run-time execution

Tag control data

If (accessing_control_data && legal_tag)

Continue

Else

raise exception

```

Figure 6 Algorithm of Dynamic Solutions

In order to validate (and identify) the integrity of data, it is necessary to have a tag (metadata) associated with the data. This "metadata" will allow us to check the integrity of data by validating the tag. To differentiate the approaches we will compare four components of dynamic solutions:

- Underlying assumptions of the approach

- Creation of metadata

- Validation of metadata

- Handling of invalid data

We provide several examples to illustrate the components.

### Example 1,

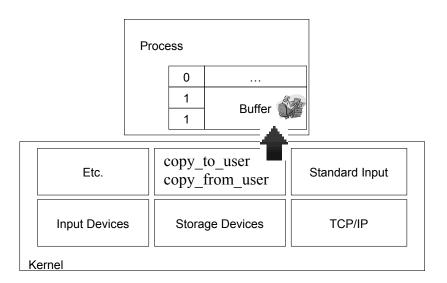

In this first example, buffer overflows are foiled by preventing any input (including buffers) from being used as control data. Metadata is used to tag data as input. When any

data is used by control instructions (e.g. jump, call, or return), the instructions must verify

that it is not input (by verifying the metadata). If it is input, an exception is raised.

From this example, we can derive the main concepts as:

**Assumption:** Input is untrustworthy for use as control data.

Creation: All functions that send or receive data from another process must set the

metadata tag of data as untrustworthy input.

Validation: Control instructions must validate that the associated control data is not

tagged.

**Handling:** Exception is raised.

Example 2,

In this second example, return addresses can only be created by call instructions. When a

return address is created, it must be tagged by the call instruction. Other instructions must

clear the metadata tag. A return instruction must verify that the address has a valid tag

(not modified by other instruction) before executing the return. If the return address is

invalid, an exception is raised.

From this example, we can derive the main concepts as:

**Assumption:** The validity of return addresses must be maintained.

**Creation:** Call instruction must set the tag of the return address.

**Validation:** Return instruction must validate that the return address is tagged.

**Handling:** Exception is raised.

14

The two examples are different in that their solutions are based on different assumptions. However, they share the same idea that a tag (or metadata) is necessarily attached to critical data. They differ in that the first example tags input in general while the second example specifically tags return addresses.

Dynamic methods can also be differentiated in how the metadata is stored. In general, there are two types of metadata: hardware supported and software managed metadata. Hardware solutions require modification of either the hardware organization, the instruction set architecture or both. For software managed metadata, the metadata is (mostly) managed by software as normal data. In general, prologue and epilogue are inserted to the program for the creation, validation and handling of metadata.

Using these components we can broadly classify dynamic solutions into four groups:

- Address Protection

- Input Protection

- Bounds Checking

- Obfuscation

The address protection schemes such as Example 2 share the assumption that addresses (e.g. return address) are critical data and must be tagged. In these schemes the metadata is created by functions that create the address (e.g. call instruction), and verified by the many instructions that use the address (e.g. return instruction). The schemes within this group are differentiated by the types of metadata they use.

The input protection schemes such as Example 1 assume that external data are untrustworthy and should not be used as internal control data. The underlining concept is that "All input is evil until proven otherwise" [32]. In most cases, metadata are tightly coupled to the data in hardware (e.g. tagged memory). Data from external sources are tagged so it can be recognized, if there is an attempt to use it as control data. The schemes in this group differ in the management of metadata.

Rather than tagging data, bounds checking schemes explicitly bound buffers to prevent overflow. In this case, the metadata is associated with every block of allocated data and is used to bound accesses

Instead of protecting the data directly, obfuscation schemes reorganize memory to obscure memory making malicious manipulation of memory through buffer overflows more difficult. These schemes assume that attackers rely on a certain snapshot of addresses to overflow the critical data. If the snapshot is random or difficult to guess, an attack is more difficult

### 2.2.3 Isolation

Isolation schemes limit the damage from attacks rather than preventing attacks. As a result their protection is not limited to buffer-overflow attacks. This category includes sandboxing and confinement schemes.

Isolation schemes isolate the attacker either to eliminate an attack vector or to contain damage after a successful attack. Preventing the execution of code in stack memory

isolates the stack from the attacker. Alternatively, limiting the memory of a process can isolate a compromised process. NX nonexecutable memory is an example of the former while sandboxing is an example of the latter.

As with dynamic solutions, isolation can be implemented purely in software or with support from hardware.

## 2.2.4 Summary of Protection schemes

In this section, we introduced a classification of buffer overflow protection into three broad categories: fixing the function, protecting the data, or limiting the effects. In this paper, we refer to these schemes as Static Analysis, Dynamic Solutions and Isolation respectively. For illustration, we draw a taxonomy in Figure 7, and will continue to review various proposed solutions in the next section.

Figure 7 Taxonomy of solutions against buffer-overflow attacks

## 2.3 Static Analysis

A number of tools examine source code to detect for possible buffer overflow vulnerabilities. The method can be a simple string matching algorithm, a lexical analyzer, or a scanner (parser). Static Analysis allows a programmer to prevent the problem before deploying the program. However, the static analysis has no runtime information. As a result, it might not be able to evaluate all possible problems and may generate false alarms. No matter how good the static analysis tool is, a programmer, eventually, has to make a final decision in correcting the program logic.

## 2.3.1 Lexical Analysis

*ITS4:* Researchers at Reliable Software Technologies developed a static analysis tool for detecting security vulnerabilities in C and C++ and named it *It's the Software Stupid!* (ITS4 [74]). The tool uses lexical analysis and matches tokens with known vulnerable functions in a pre-defined database. It is useful for highlighting potential security problems as code is written. The report generated from ITS4 includes a brief description of the problem, a brief description of how to solve the problem, and the level of severity.

FlawFinder and RATS: FlawFinder [25] and RATS [61] are similar tools that scan source code using lexical analysis. When the developers of each team noticed that they were developing similar tools, they decided to combine the two tools into one in the future. Basically, FlawFinder uses the same method as that of ITS4. However, the report generated from FlawFinder is associated with the values of the parameters of the function. For example, variable strings are considered more risky than constant strings. In addition to C, RATS also supports Perl, PHP and Python source code.

**STOBO:** This Systematic Testing Of Buffer Overflow (STOBO [30]) is an interesting static analysis tool for C programs. It uses profiling to generate its report. This tool will insert special functions into the original program to keep track of each variable and memory allocation. Running the modified program will provide dynamic analysis from the runtime environment.

*LibSafe:* LibSafe [2] is the implementation of static analysis in the run time environment. It is a safe implementation of a library that is forced to be loaded before the standard C library. Since the library is accessed in the order of loading, Libsafe is able to intercept the known vulnerable functions (e.g. strepy, streat).

Dynamic Tainted Analysis: Dynamic Tainted Analysis [50] is a monitor tool modified for examining the arguments and results of each system call, and determines whether data should be marked as input. The current implementation is in Valgrind, a Linux tool for detecting memory management problems. Memory is emulated for tracking the information flow (using a tainted bit associated to each byte). System calls are monitored and recording. According to the policy, some system call may generate the tainted data. All arithmetic instructions are captured to propagate the tainted. This tool is useful in that it uses dynamic information for fixing the program.

### **Potential Problems:**

- False alarms

- Does not handle buffer overflow in user-defined functions and macros

## 2.3.2 Semantic Analysis

*Splint:* Splint [24] is a tool for statically checking C programs for security vulnerabilities and coding mistakes. The name and some of its functionality originates from a popular static analysis tool for C called Lint released in the seventies. Splint uses a parser to perform semantic analysis. This means that the tool has a better chance of differentiating between correct and incorrect use of functions than those based on lexical analysis.

**Boon:** BOON [75] is another tool for statically checking C programs for security vulnerabilities. Boon treats the C String as an abstract data type, and models buffers with two integer ranges. These two ideas provide a framework for the analysis.

#### **Potential Problems:**

- False alarms

- Does not handle buffer overflow in user-defined functions and macros

# 2.4 Dynamic Solutions

Several dynamic solutions have been introduced. Each method varies in assumption, choices of metadata and management scheme, or handling routines. We will review them in the following order: Address Protection, Input Protection, Bounds Checking, and Obfuscation. For each method, we will pinpoint the choice of metadata and the management of the metadata.

### 2.4.1 Address Protection

There are several similar methods that share the assumption of protecting the address. However, they use different types of metadata. These variations include: a canary value, tagged memory, and hardware stack. Though some solutions in this class have become

obsolete as attacks have matured, they are a good initial step in preventing buffer-

overflow attacks.

2.4.1.1 Canary Words

Assuming that corrupting an address will also corrupt the adjacent data, the validity of

address can be verified by validating special adjacent metadata (the canary word)<sup>1</sup>. The

general mechanism can be described as:

1. Place a canary word next to the address (e.g. return address) when the address is

created (e.g. by a call instruction).

2. Verify the canary word before using the address (e.g. before a return instruction

uses a return address).

StackGuard [15, 17, 18, 31]

**Assumption:** Return addresses must not be modified after creation

**Metadata:** Canary word adjacent to the return address

**Creation:** Compiler injects prologue to the header of every function for placing a canary

word next to the return address.

Validation: Compiler injects epilogue at the end of every function for validating the

canary word.

**Handling:** Compiler injects an error handling routine.

A canary word is similar to a canary in a mine: if the canary dies, that indicates a problem.

21

#### **Potential Problems:**

- Insufficient assumption: buffer-overflow attacks have changed in response to this type of protection to now attack other addresses.

- Insufficient protection for the canary word itself and the return address (See [7] for more details.)

### ProPolice [23]

ProPolice supports two mechanisms. The first one is return address protection similar to StackGuard. In addition to the return address protection, ProPolice also assumes that buffer overflow occurs only in one direction, and reorders the declaration statement to protect against function pointer attacks. Since an overflow only goes in one direction, declaration reordering can prevent the function pointer from being overflowed. Figure 8 shows the sample of the reordering process. However, this can only protect some variables from being overflowed, but not other variables that are still in the overflow direction.

| Original Code                 | Reorder Code                  |  |

|-------------------------------|-------------------------------|--|

| <pre>Int bar() {</pre>        | <pre>int bar() {</pre>        |  |

| <pre>void (* funct2)();</pre> | char buff[80];                |  |

| char buff[80];                | <pre>void (* funct2)();</pre> |  |

| •                             | •                             |  |

| }                             | }                             |  |

Figure 8 Sample of code reordered by IBM ProPolice

### 2.4.1.2 Address Encode

Knowing that encryption can help preserving the integrity of data, the same concept is applied to protect the integrity of addresses (e.g. function pointers or return addresses). In this type of protection, the metadata is the key used to encode the data. The general mechanism can be described as:

1. Encode an address with a pre-defined key before storing it to the memory.

2. Decode the address on dereferencing (loading back to the processor).

PointGuard [16] and Hardware Supported PointGuard [64, 71]

**Assumption:** Pointer must not be modified after creation.

**Metadata:** Per-process random key for encrypting pointers (generated by software or hardware supported hash table)

**Creation:** Compiler injects code for encoding pointer (with or without hardware supported instruction)

**Validation:** Compiler injects code for decoding pointer on dereferencing. Pointer to outside process boundaries is flagged as malicious.

**Handling:** Exception is raised

#### **Potential Problems:**

- (Possibly) insufficient randomness of encryption key

- Issues with arrays and compile-time assignment of pointers. Since a pointer is encoded with a per-process key that is generated when the program is loaded, it is not possible to assign a value to the pointer before the key is determined. In addition, languages (such as C, C++) may handle a string as a pointer of characters (array). It is not clear whether the string pointer should be encoded.

- Shared libraries and interprocess communication. While each process is aware of its key, the shared library is shared. Thus, passing a pointer to the shared library requires sharing a key between the main program and the shared library. Similarly, passing a pointer to another process also requires special handling for the key.

## 2.4.1.3 Copy of address

A simple method for preserving the integrity of an address is to preserve another copy of the address. The mechanism can be summarized as follow:

- 1. Create a safe copy of the address (e.g. return address) when it is created.

- 2. Verify the (return) address against the safe copy before using it (e.g. on return).

StackGhost [27]

**Assumption:** Return addresses must not be modified after creation.

**Metadata:** A copy of return addresses stored in the register window of Sun SPARC processor.

**Creation:** Hardware supported instructions automatically create a copy of the return address in the register.

Validation: Operating system validates return address with the copy in the register window

**Handling:** Operating system (OpenBSD) patch of handling routine to handle the new exception.

#### **Potential Problems:**

- Insufficient assumption: overflow attacks have changed in response to this type of protection to now attack other addresses.

- Dynamic update of return addresses (e.g. non-LIFO control flow).

- Overflow of register window.

- Architecture specific.

### RAS [44, 78, 79]

**Assumption:** Return address must not be modified after creation.

**Metadata:** A copy of return addresses stored in the Return Address Stack (RAS)—a hardware accelerator technique in some processors

**Creation:** Hardware supported instructions automatically create an entry of a return address in Return Address Stack (RAS)

**Validation:** Compiler injects prologue for validating the return address against the copy before the return instruction.

**Handling:** Exception is raised.

**Potential Problems:**

Insufficient assumption: overflow attacks have changed in response to this type of

protection to now attack other addresses.

• Dynamic update of return addresses (e.g. non-LIFO control flow).

• Overflow of return address stack.

• Architecture specific.

Split Stack [78]

**Assumption:** Return address must not be modified after creation.

Metadata: A special memory area for storing the return address (control stack)

separately from the regular data stack. Note that this can be implemented as either

software or hardware.

Creation: Software: compiler injects epilogue to call instruction for storing the return

address in a control stack (software). Hardware: the semantics of the call instruction are

modified to store the address.

**Validation:** Software: compiler injects prologue to return instruction for restoring the

return address from the control stack,, or Hardware: the semantics of the return

instruction are modified.

**Handling:** Compiler injects handling routine (software) or exception is raised (hardware).

**Potential Problems:**

• Insufficient assumption: overflow attacks have changed in response to this type of

protection to now attack other addresses.

• Dynamic update of return addresses (e.g. non-LIFO control flow).

• Breaking of system programs that assume the layout of the stack frame.

SmashGuard [53]

**Assumption:** Return address must not be modified after creation.

**Metadata:** A hardware stack for storing a copy of return address.

Creation: The semantics of the call instruction are modified to push a copy of return

address onto the hardware stack.

**Validation:** The semantics of the return instruction are modified to pop and compare the

two return addresses.

**Handling:** Exception is raised.

**Potential Problems:**

Insufficient assumption: overflow attacks have changed in response to this type of

protection to now attack other addresses.

• Dynamic update of return addresses (e.g. non-LIFO control flow). In the paper,

the authors extend functionality of stack to cover some aspects of this issue.

• Breaking of system programs that assume the layout of the stack frame.

RAD Compiler [12], RAD Binary Rewrite [59] and DISE [14]

RAD Compiler, RAD Binary Rewrite and DISE share the same concept of storing a

redundant copy of return addresses for preserving the integrity of the return address.

However, the mechanisms for injecting the protection code are slightly different. In RAD

Compiler [12], the compiler is responsible for embedding the protection code into the

program. In RAD Binary Rewrite [59], the loader is responsible for injecting the

protection code using binary rewrite. For DISE [14], the hardware-assisted

implementation, dynamic instruction stream editing, will expand the instructions on the

fly. Due to the similarity, we will only elaborate the details of RAD Binary Rewrite [59].

**RAD Binary Rewrite**

**Assumption:** Return address must not be modified after creation.

**Metadata:** A special memory area for storing a redundant copy of return addresses

(Return Address Repository, RAR) which is protected by the *mprotect()* system call to

mark the area as read-only [12].

Creation: Loader performs binary rewrite to inject prologue to the header of every

function for storing a copy of the return address in RAR.

Validation: Loader performs binary rewrite to inject epilogue to the end of every

function for validating the return address with a redundant copy.

**Handling:** Loader performs binary rewrite to inject a new exception handing routine.

**Potential Problems:**

Insufficient assumption: overflow attacks have changed in response to this type of

protection to now attack other addresses.

• Dynamic update of return addresses (e.g. non-LIFO control flow).

• Performance issue of the *mprotect()* system call.

StackShield [73]

There are three mechanisms proposed in StackShield: Global Ret Stack, Ret Range

Check, and Function Pointer Protection. The first two mechanisms are similar concepts,

but differ slightly in implementation. We will present the first two together and the

pointer protection separately.

Global Ret Stack and Ret Range Check

**Assumption:** Return address must not be modified after creation.

Metadata: A special memory area for storing a redundant copy of return addresses

(Global Array).

Creation: Compiler injects prologue into the header of every function for copying the

return address to the Global Array.

Validation: Compiler injects epilogue into the end of every function for copying the

return address from the Global Array back to the original location without checking

(Global Ret Stack) or for validating the return address with a redundant copy (Ret Range

Check).

**Handling:** Compiler injected exception handling routine.

**Function Pointer Protection**

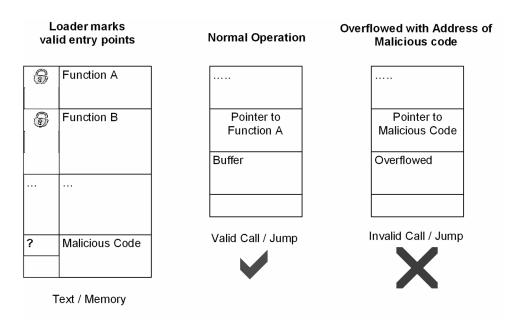

**Assumption:** Function Pointer must only point to a location in the text (code) segment.

**Metadata:** The range of the code segment.

**Creation:** Loader creates the code segment.

Validation: Compiler injects prologue to each function pointer for validating that its

value must be in the valid range.

**Handling:** Compiler injected exception handling routine.

**Potential Problems:**

Insufficient assumption: overflow attacks have changed in response to this type of

protection to now attack other addresses.

• Insufficient protection for the metadata itself and the return address (See [7] for

more details.)

• Dynamic update of return addresses (e.g. non-LIFO control flow).

## LibVerify [2]

LibVerify is a type of dynamic solutions that is implemented via binary rewrite. Figure 9 shows the mechanism.

**Assumption:** Return address must not be modified after creation.

**Metadata:** A special memory area for storing a redundant copy of return addresses.

**Creation:** Loader performs binary rewrite to create a copy of secure code by injecting a prologue for storing return addresses in the special memory area.

**Validation:** Loader performs binary rewrite to inject epilogue for verifying the return address.

Handling: Loader performs binary rewire to inject handling routine.

#### **Potential Problems:**

• Insufficient assumption: overflow attacks have changed in response to this type of protection to now attack other addresses.

void new\_main() { char buffer[96]; ▼ 0xbfffffb heap strcpy(buffer, large\_string); env. vars region // jump to wrapper exit bottom of stack parameters return addr expected location of the void main() // jump to wramper\_entry char buffer[96]; return addr stack vars text strcpy(buffer, large\_string); region \_return; ddr of the buffer attack code overflow frame pointer→ wrapper\_entry() { // store return address, // jump to new\_main/ attack code binary rewrite wrapper\_exit() { < library stack pointer // verify return address // return

Dynamic update of return addresses (e.g. non-LIFO control flow).

Figure 9 LibVerify. (From [2])

stack address space

**SCACHE** [35].

**Assumption:** Return address must not be modified after creation.

**Metadata:** Cache memory.

**Creation:** Hardware creates replica cache line for each return address store.

**Validation:** Hardware compares the return address loaded from stack with the replica in

the cache line.

**Handling:** Exception is raised.

**Potential Problems:**

Insufficient assumption: overflow attacks have changed in response to this type of

protection to now attack other addresses.

• Complexity of cache replacement algorithm.

• Dynamic update of return addresses (e.g. non-LIFO control flow).

2.4.1.4 Tags

Tagged Architecture [28]

Tagged memories go back at least thirty years with many proposed architectures and a

few which made it to market. For our purposes, tagged-memory architectures provide

three main functions. The first supports language and the Symbolics [47] Lisp computer,

which achieved a relatively short-lived commercial success, is a classic example. In that

computer, the tags were used to efficiently keep track of dynamic types. The second type

uses tags to support capabilities. Capabilities reach back forty years, and their popularity

has increased recently with increased interest in security exemplified by capability-based

operating systems such as EROS [65]. The tags support the capabilities which control

access. The third is best exemplified by the IBM System/38 [21] database computer (the

predecessor of the IBM AS/400) which used a tag to protect pointers. Of those, it is the

IBM System/38 that is relevant to this survey.

Here, we will present the concepts embedded in the IBM System/38 as a representative of

protection against buffer-overflow attacks provided by tagged architecture in general.

**IBM System/38 [21]**

**Assumption:** Return address and function pointer must not be modified after creation.

**Metadata:** A bit associated with each word (or byte) of memory.

Creation: Call instruction and a special instruction set the tag of a return address and a

function pointer respectively.

Validation: Return instruction and branch instruction validate the tag bit of a return

address and a function pointer.

**Handling:** Exception is raised.

**Potential Problems:**

Compatibility

Performance

2.4.2 Input Protection

Some methods assume that input data should be treated differently from local data. The

idea is that input should not be used as control data. We will review three methods,

Minos [19, 20], Tainted Pointer [4], and Dynamic Flow Tracking [67] that share the same

assumption, but different implementations. Minos views data across segments as input.

Tainted Pointer considers data passed from the operating system as input. Dynamic Flow

Tracking relies on operating systems for marking input. Note that Secure Bit treats data

passing between processes through the kernel as input.

Minos [19, 20]

**Assumption:** Input (low-integrity data) must not be used as control data.

**Metadata:** A bit associated to each word (or byte) of memory.

**Creation:** A reserved bit in a descriptor is used to indicate whether data is moving across

segments (rings) and marks the data as low integrity (set the tag) or carries the tag over.

All 8-bit and 16-bit load operations and floating point, MMX, BCD, and similar

extensions mark the data as low integrity. In addition, data that is accessed after the ctime

established by the kernel and some system calls (e.g. exec, pread) will force the data to be

low integrity.

**Validation:** Jump, Call or Return instructions validate that control data are low integrity.

**Handling:** Exception is raised.

**Potential Problems:**

Possible issues with multi-threading program (e.g. Sun Java JVM). To solve the

issue, some programs may have to be executed in a "compatibility mode" which

has no protection.

Tainted Pointer [10]

**Assumption:** Input must not be used as control data.

**Metadata:** A bit associated to each byte of memory (tainted bit).

Creation: The current implementation is in a hardware simulator (SimpleScalar) which

modifies SimpleScalar I/O functions (SYS READ and SYS RECV) to mark every byte

coming into a process as tainted. ALU instructions are modified to propagate the

taintedness. (Note that compare instructions will untaint every byte in the operands of the

instruction.)

**Validation:** Jump instructions validate the pointer.

**Handling:** Exception is raised

**Potential Problems:**

Since the current implementation is in a hardware simulator some operating

system issues are not yet resolved. For example, there are potential issues with

multi-threading program (e.g. Sun Java JVM).

• Issues with compare instruction. Since the compare instruction can be used to

untaint data that opens a vector for attack.

Dynamic Flow Tracking [67]

**Assumption:** Input must not be used as control data.

**Metadata:** A bit associated to each byte of memory (tainted bit).

Creation: The current implementation is in a hardware simulator (SimpleScalar) which

modifies SimpleScalar I/O functions (SYS READ and SYS RECV) to mark every byte

coming into a process as tainted. ALU instructions are modified to propagate the

taintedness

**Validation:** Jump instructions validate the pointer.

**Handling:** Exception is raised

**Potential Problems:**

Since the current implementation is in a hardware simulator some operating system issues are not yet resolved. For example, there are potential issues with

multi-threading program (e.g. Sun Java JVM).

2.4.3 Bounds Checking

In Bounds Checking, the methods assume that all accesses to data must be done within

the boundary of that variable. We will review two main approaches: software and

hardware approaches. For the software, the implementation can be a modification to the

compiler of current languages or virtual machine solutions (e.g. type-safe programming

languages).

Array Bounds Checking [37]

Researchers from Imperial College, London [37] created a backward compatible bounds

checking in C. The method does not change the representation of a pointer. Thus, it is

compatible with the standard C library. For every pointer, a base pointer is defined. A

pointer value is valid for only one memory region. Checking whether the reference is in

the same region as the one referred by a base pointer enforces bounds checking. This

method is useful to prevent buffer overflow attacks. However, with the overhead of a

symbol table used to keep track of each pointer, it experiences more than a 30 times

slowdown in a pointer-intensive program. As a result, this tool is ideal for debugging, but

may not be suitable for most applications. Similar tools include *Rational PurifyPlus* [60],

and BoundsChecker [6]. Conceptually, we can view this approach as a software

implementation of segmentation which uses an entry in the symbol table as a segment

descriptor.

**Assumption:** Accessing a memory area must be in a boundary.

**Metadata:** A descriptor attached to each pointer and memory allocation.

**Creation:** Compiler generates descriptor for each pointer and allocation.

**Validation:** Compiler injects prologue for checking pointer and array boundary.

**Handling:** Handling routine

**Potential Problems:**

Performance issue (30X).

• Compatibility with legacy code (with respect to the presentation of pointer and

Nested structure of memory.

**Segmentation:** Limited hardware protection has existed in various processors for many

years. Among them, segmentation is a novel one. Segmentation is primarily used as a

mechanism to support the relocation of memory. In the early implementation of

segmentation, a base register is required for each memory access. IA-32 and I432 [52]

also adopt the idea and associate segmentation with base address, boundary check, and

rings. Explicitly declaring and referring every buffer with base and boundary,

segmentation can protect against buffer-overflow attacks. A drawback of segmentation is

the extra storage for storing segment descriptors. In IA-32, every memory access (in

protected mode) requires a base and limit. However, most operating systems bypass

segmentation by setting one large segment for whole memory in order to maintain

portability and gain better performance. I432 was a CISC architecture that is designed

with security awareness. Based on the paradigm of the ADA programming language, it

checks every data boundary and forces every function call to create a new domain

(segment). Since I432 instructions are bit encoded, ranging from six to 321 bits,

computation took 10 to 20 times as long as the contemporary VAX 11/780 [13].

Consequently, I432 was a commercial failure.

A similar concept can also apply to a function pointer. For example, one of the 1960s

architecture, ICL 2900 series systems [28], had a native hardware 'pointer' type (a.k.a.

descriptor) that included in it the size of the object pointed to. The hardware would check

that any dereferences were not out of bounds.

**Assumption:** Accessing a memory area must be within a boundary.

**Metadata:** Hardware supported descriptor registers.

Creation: Compiler generates descriptor for each memory allocation via supported

management from the operating system.

**Validation:** Hardware supported bound checking though a descriptor.

**Handling:** Exception is raised.

**Potential Problems:**

Performance issue

• Nested structure of memory

Type-safe programming languages and interpreted languages: In the type-safe

programming languages and interpreted languages (e.g. Java, .Net), the metadata and

bounds checking process is embedded into the virtual machine. Correct bounds checking

can prevent buffer overflows. However, the virtual machine itself is written in C/C++ so

somehow the virtual machine has to interact with underlying components which use type-

unsafe languages. Type-safe languages decrease the probability of being attacked, but can

still be exploited by buffer overflows. For example, there have been buffer-overflow

attacks in Java [22, 68], Perl [72], etc. There also exists a type-safe C: CCured [48].

**Assumption:** Accessing a memory area must be within a boundary.

**Metadata:** A descriptor attached to each variable.

**Creation:** Virtual machine generates a descriptor for each memory allocation.

**Validation:** Virtual machine validates every single memory access.

**Handling:** Virtual machine handles the exception.

**Potential Problems:**

Performance issue

• Complexity of Garbage Collector (if applicable)

• Compatibility with legacy code

2.4.4 Obfuscation

When there is no appropriate solution, confusion and increased difficulty can be used as a

protection mechanism. However, it should not be used alone when other methods are

applicable [8].

Address Obfuscation

Conceptually, Address Obfuscation [3] reorganizes the memory area of each process to

make it difficult for attackers. Facing a changed the memory alignment, malicious users

will encounter difficulty in overwriting the expected addresses. A compiler is modified to

randomize the base addresses of each memory segment, the distances between each pair

of data items, and permutes the order of variables/routines. A similar mechanism is

implemented in the Address Space Layout Randomization (ASLR) schema of the PAX

project [54]. In the big picture, this method cannot protect against skilled attackers who

obtain the binary of the program. Since the randomness does not occur during execution,

a dissembler tool will unveil the necessary information.

**Assumption:** Buffer-overflow attacks assume a specific layout of memory snapshot.

**Metadata:** Offset added to each variable for accessing each data.

**Creation:** Compiler generates offset value for each variable.

Validation: None

Handling: None

**Potential Problems:**

Randomness of the offset value

2.4.5 Isolation

There are two main ideas behind isolation. The first is to limit the execution of code that

may result from buffer-overflow attacks. Another idea is to sandbox the whole process

from accessing certain system resources based on a predefined policy. Apart from these

two main ideas, variations include the isolation of executable code from being installed or

modified in the run-time environment.

Non-Executable Memory

Another common technique is non-executable partitions of memory such as pages or segments. Many non-X86 processors such as SPARC support non-executable memory, and AMD has recently added a similar feature named "NX" [41]. Non-executable memory prevents code in the buffer on the stack from being executed, effectively protecting against a class of buffer overflow attacks that results in the execution of code on the stack. The Solar Designer group [66] and INGO [34] also proposed a patch to the Linux kernel to make a *non-executable stack*. However, the integrity of the return address is not protected—leaving the system vulnerable to attacks using the address of either a resident shell or code in the heap. In certain cases, such as signal handler return on Linux, the system requires an executable stack in order to function properly. Moreover, any LISP-like functional language requires an executable stack in their normal operation (aka. trampoline). As a result, this method only protects against a narrow range of attacks.

SPEF: Alternatively, researchers from Microsoft and the University of California at Los Angeles have developed a Secure Program Execution Framework [40] (SPEF). Instead of protecting the data, the method protects the code. The method aims at making a system difficult to inject malicious code. SPEF is a platform that consists of architectural mechanisms and compilation tools. The installation of a program requires both encryption and transformation. As a result, injecting the malicious code is not simple and requires a special process. This method prevents the injection of malicious code. Obviously, it is still possible to overflow the buffer and modify the return address or the function pointer to point to a known address. Based on 3DES and domain ordering hardware, SPEF should experience performance difficulties and may not be feasible for

general applications. Another implementation that shares the same concept but uses instruction block signature is [46]

Instruction-Set Randomization: Similar to SPEF, Instruction-Set randomization [38] introduces difficulty in injecting the malicious code. The General idea is to randomize the coding of instructions by XORing them with a key. The authors propose a per-process key schema which makes it difficult for a dynamic-linked library. As a result, the method supports only static-linked libraries. The technique can also be applied to scripting languages by adding a random number at the end of each instruction and modifying the virtual machine to validate the number in each instruction. In [38], an example of random Perl is presented. The drawbacks are the lack of support for dynamic-linked libraries, the requirement of special hardware, and the limitation of using polymorphic and self-modifying code. Like SPEF, which only prevents the injection of malicious code, overflowing with a known address is possible.

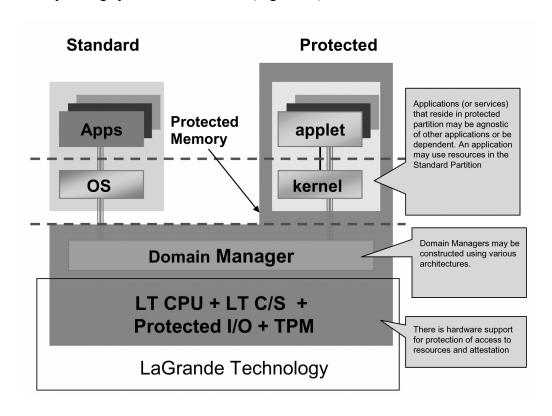

Sandboxing: Sandboxing is a policy-enforcement mechanism. Since buffer-overflow occurs when information is passed from one domain to another domain, sandboxing a process intuitively cannot prevent such attacks. With appropriate policy rules, it is, however, possible to limit the damage of buffer-overflow attacks. Sandboxing can be done at several levels: kernel level [55], user level [9], or even hardware-supported sandboxing (e.g. Intel LaGrande [36], TCPA [43, 70], TrustZone [1], Microsoft NGSCB [45], ChipLock [39], Bear [43].) Like tagged memory, there exists a very fine-grained approach to memory management (e.g. MMP [77]), but such approaches can be

successful for buffer-overflow protection only if a perfect combination of a security policy and an implementation exists. We believe that it is complementary to other techniques rather than a replacement.

## 2.5 Analysis

With the knowledge of buffer overflow attacks in hand, we will raise issues critical to protections against buffer-overflow attacks. Those issues are: Common Pitfalls, Performance, Compatibility (Transparency), and Deployment and Cost.

#### 2.5.1 Pitfalls

Buffer-overflow prevention, like many security efforts, has been an "arms-control race" in that attacks have evolved to counter prevention schemes which in turn require increased sophistication in prevention. In hindsight, we can look back and see why earlier efforts failed. Two themes have emerged:

**Insufficient assumptions:** Some approaches only provide protection against a subset of buffer-overflow attacks. This is due to the maturing of buffer-overflow attacks that have shifted their target from one address to another. For example, the best known type of buffer-overflow attack modifies return-addresses. As soon as developers tried to protect the return address, function-pointer attacks became popular. Another example is trusted code. It can be wrong to assume that trustworthy code is 100% safe from buffer-overflow attacks. Compromising the signed code or the signing mechanism allows execution of malicious 'trusted' code.