# Computer Architecture and Engineering Lecture 7: Divide, Floating Point, Pentium Bug

September 17, 1997

Dave Patterson (http.cs.berkeley.edu/~patterson)

lecture slides: http://www-inst.eecs.berkeley.edu/~cs152/

# **Outline of Today's Lecture**

- Recap of Last Lecture and Introduction of Today's Lecture (4 min.)

- ° Divide (20 min.)

- Questions and Administrative Matters (2 min.)

- ° Floating-Point (25 min.)

- Questions and Break (5 min.)

- ° Pentium Bug [Patterson] (25min.)

cs 152 | 17 Divide, FP. 2

# Recap of Last Lecture: Summary

- ° Intro to VHDL

- entity = symbol, architecture ~ schematic, signals = wires

- behavior can be higher level

- x <= boolean\_expression(A,B,C,D);</li>

- On-line Design Notebook

- Open a window with editor, or our tool, => cut&paste

- Multiply: successive refinement to see final design

- 32-bit Adder, 64-bit shift register, 32-bit Multiplicand Register

- Booth's algorithm to handle signed multiplies

- There are algorithms that calculate many bits of multiply per cycle (see exercises 4.36 to 4.39 in COD)

- ° Shifter: well...

- What's Missing from MIPS is Divide & Floating Point Arithmetic:

Next time the Pentium Bug

# Recap: VHDL combinational example

```

ENTITY nandnor is

GENERIC (delay: TIME := 1ns);

PORT (a,b: IN VLBIT; x,y: OUT VLBIT)

END nandnore

ARCHITECTURE behavioral OF nandnor is

BEGIN

x <= a NOR b AFTER delay;

y <= a NAND b AFTER delay;

END behavioral;

```

cs 152 I7 Divide,FP.4 DAP ©UCB 1997

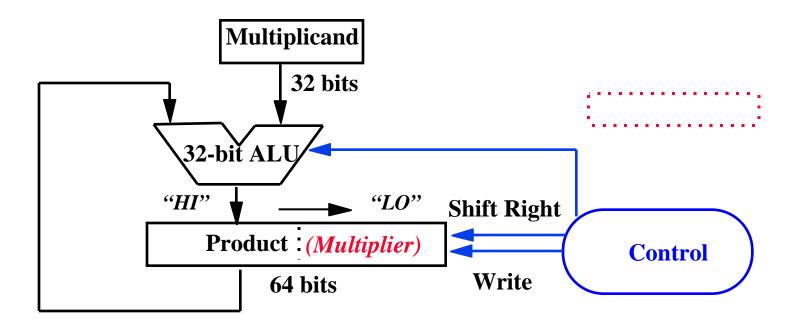

### **Review: MULTIPLY HARDWARE Version 3**

32-bit Multiplicand reg, 32-bit ALU,

64-bit Product reg (shift right), (0-bit Multiplier reg)

# **Review: Booth's Algorithm Insight**

| <b>Current Bit</b> | Bit to the Right | Explanation              | Example             |

|--------------------|------------------|--------------------------|---------------------|

| 1                  | 0                | Beginning of a run of 1s | 000111 <u>10</u> 00 |

| 1                  | 1                | Middle of a run of 1s    | 00011 <u>11</u> 000 |

| 0                  | 1                | End of a run of 1s       | 00 <u>01</u> 111000 |

| 0                  | 0                | Middle of a run of 0s    | 0 <u>00</u> 1111000 |

Originally for Speed since shift faster than add for his machine

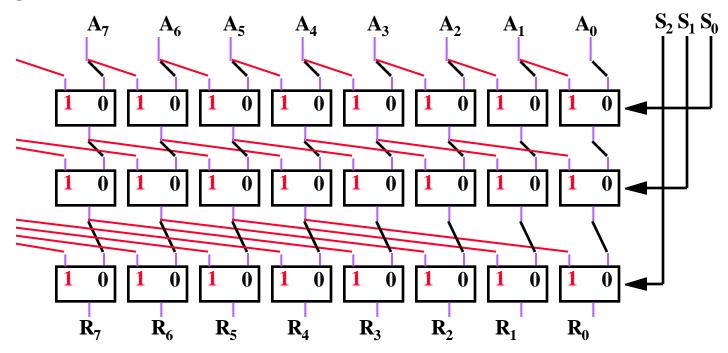

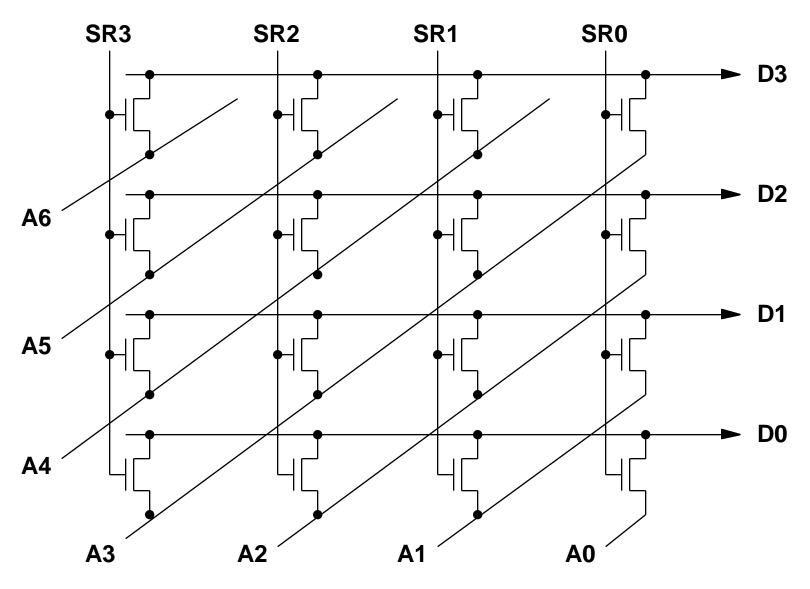

## **Review: Combinational Shifter from MUXes**

8-bit right shifter

- ° What comes in the MSBs?

- o How many levels for 32-bit shifter?

- ° What if we use 4-1 Muxes ?

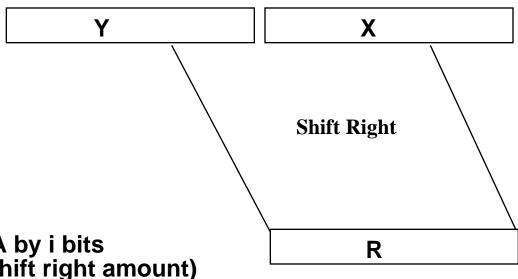

#### **Funnel Shifter**

#### Instead Extract 32 bits of 64.

- ° Shift A by i bits (sa= shift right amount)

- $^{\circ}$  Logical: Y = 0, X=A, sa=i

- ° Arithmetic? Y = \_, X=\_, sa=\_

- ° Rotate? Y = \_, X=\_, sa=\_

- ° Left shifts? Y = \_, X=\_, sa=\_

## Technology-dependent solutions: transistor per switch

cs 152 I7 Divide,FP.9

# **Divide: Paper & Pencil**

```

Divisor 1000 1001010 Dividend

-1000 10 101 1010 1010 -1000 10 Remainder (or Modulo result)

```

See how big a number can be subtracted, creating quotient bit on each step

Binary => 1 \* divisor or 0 \* divisor

3 versions of divide, successive refinement

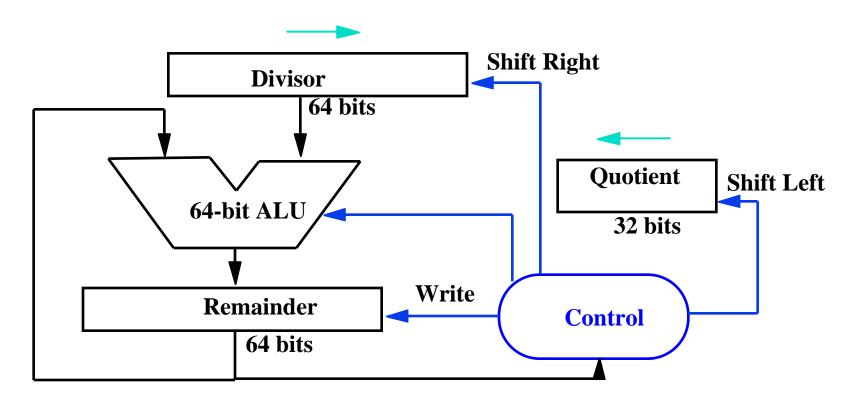

#### **DIVIDE HARDWARE Version 1**

64-bit Divisor reg, 64-bit ALU, 64-bit Remainder reg,

32-bit Quotient reg

cs 152 I7 Divide,FP.11 DAP ©UCB 1997

# **Divide Algorithm Version 1**

**Start: Place Dividend in Remainder**

°Takes n+1 steps for n-bit Quotient & Rem. |

Remainder Quotient Divisor 0000 0111 0000 0010 0000

1. Subtract the Divisor register from the Remainder register, and place the result in the Remainder register.

Remainder  $\geq 0$

Test Remainder < 0

Remainder

2a. Shift the Quotient register to the left setting the new rightmost bit to 1.

2b. Restore the original value by adding the Divisor register to the Remainder register, & place the sum in the Remainder register. Also shift the Quotient register to the left, setting the new least significant bit to 0.

3. Shift the Divisor register right1 bit.

n+1 repetition2 No: < n+1 repetitions

Yes: n+1 repetitions (n = 4 here)

**Done**

#### **Observations on Divide Version 1**

- 1/2 bits in divisor always 0

=> 1/2 of 64-bit adder is wasted

=> 1/2 of divisor is wasted

- ° Instead of shifting divisor to right, shift remainder to left?

- 1st step cannot produce a 1 in quotient bit (otherwise too big)

=> switch order to shift first and then subtract, can save 1 iteration

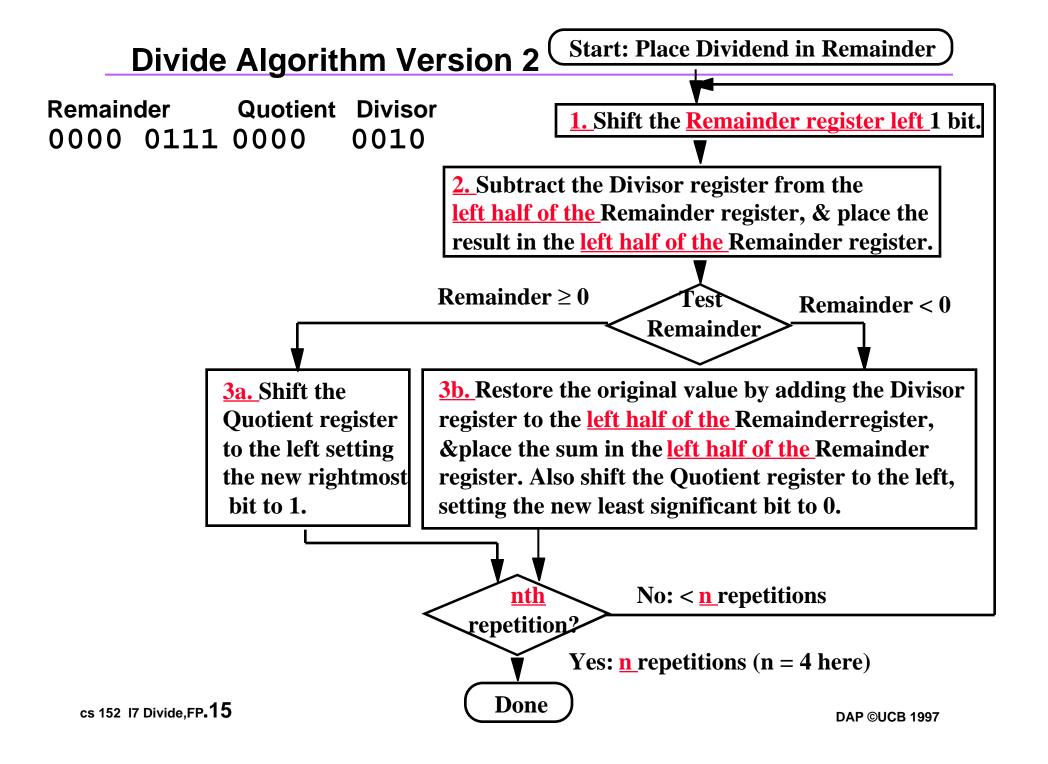

### **DIVIDE HARDWARE Version 2**

° 32-bit Divisor reg, 32-bit ALU, 64-bit Remainder reg, 32-bit Quotient reg

cs 152 I7 Divide,FP.14 DAP ©UCB 1997

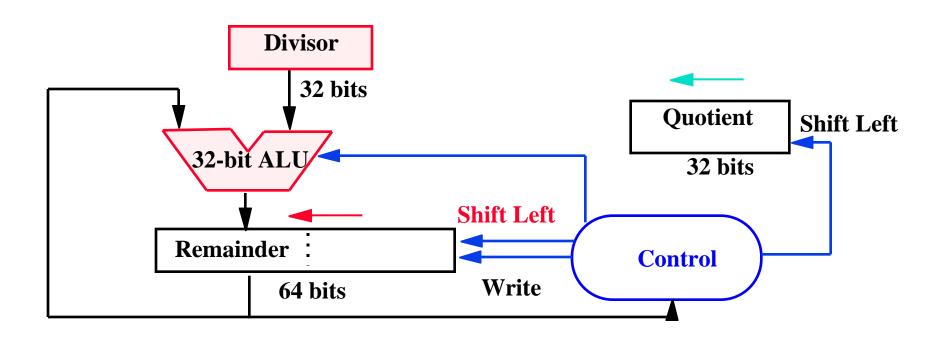

### **Observations on Divide Version 2**

- Eliminate Quotient register by combining with Remainder as shifted left

- Start by shifting the Remainder left as before.

- Thereafter loop contains only two steps because the shifting of the Remainder register shifts both the remainder in the left half and the quotient in the right half

- The consequence of combining the two registers together and the new order of the operations in the loop is that the remainder will shifted left one time too many.

- Thus the final correction step must shift back only the remainder in the left half of the register

cs 152 I7 Divide,FP.16 DAP ©UCB 1997

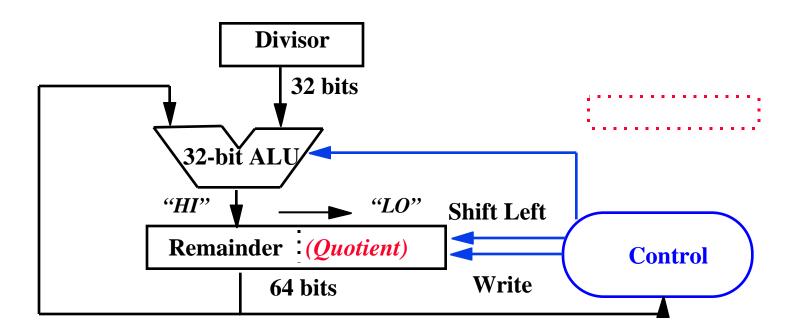

### **DIVIDE HARDWARE Version 3**

° 32-bit Divisor reg, 32 -bit ALU, 64-bit Remainder reg, (0-bit Quotient reg)

cs 152 I7 Divide,FP.17 DAP ©UCB 1997

#### **Observations on Divide Version 3**

- Same Hardware as Multiply: just need ALU to add or subtract, and 63-bit register to shift left or shift right

- Hi and Lo registers in MIPS combine to act as 64-bit register for multiply and divide

- Signed Divides: Simplest is to remember signs, make positive, and complement quotient and remainder if necessary

- Note: Dividend and Remainder must have same sign

- Note: Quotient negated if Divisor sign & Dividend sign disagree e.g.,  $-7 \div 2 = -3$ , remainder = -1

- Possible for quotient to be too large: if divide 64-bit interger by 1, quotient is 64 bits ("called saturation")

### **Administrative Matters**

- ° Midterm Wednesday 10/1

- Revise deadlines (so that can dicuss in section):

Book exercises Fridays at noon

Labs on Tuesdays at noon

- ° Finishing Chapter 4 today, moving to Chapter 5 Friday

- ° ALU + notebook, teams of 2 next lab

cs 152 I7 Divide, FP. 20

# **Floating-Point**

What can be represented in N bits?

| ° Unsigned           | 0                  | to   | 2            |     |

|----------------------|--------------------|------|--------------|-----|

| ° 2s Complement      | - 2 <sup>N-1</sup> | to   | N-1<br>2 - 1 |     |

| ° 1s Complement      | N-1<br>-2+1        | to   | 2-1          | N-1 |

| ° Excess M           | -M                 | to N | 2 - M - 1    |     |

| • (E = e + M)  ° BCD | N/4                | to   | 10 - 1       |     |

- ° But, what about?

- very large numbers?

- 9,349,398,989,787,762,244,859,087,678

- very small number?

- 0.00000000000000000000045691

rationals

2/3

irrationals

**√ 2**

• transcendentals

**e**, π

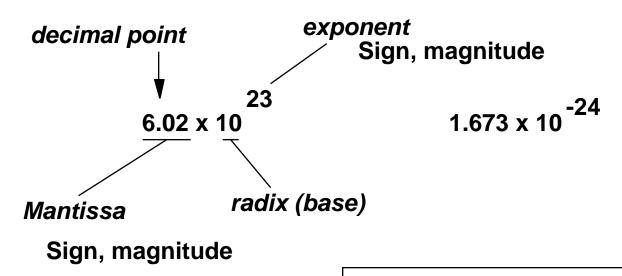

## **Recall Scientific Notation**

IEEE F.P. ± 1.M x 2<sup>e - 127</sup>

#### ° Issues:

- Arithmetic (+, -, \*, /)

- Representation, Normal form

- Range and Precision

- Rounding

- Exceptions (e.g., divide by zero, overflow, underflow)

- Errors

- Properties (negation, inversion, if A ≠ B then A B ≠ 0)

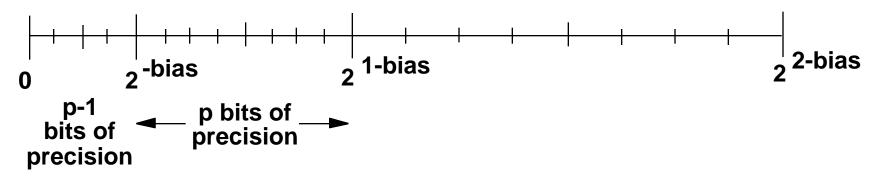

# Review from Prerequisties: Floating-Point Arithmetic

Representation of floating point numbers in IEEE 754 standard:

single precision

exponent: excess 127 binary integer

mantissa: sign + magnitude, normalized binary significand w/ hidden

actual exponent is e = E - 127

integer bit: 1.M

$$N = (-1)^{S} 2^{E-127} (1.M)$$

$$0 = 0 \ 000000000 \ 0 \dots 0$$

$-1.5 = 1 \ 011111111 \ 10 \dots 0$

Magnitude of numbers that can be represented is in the range:

$$2^{-126}$$

(1.0) to  $2^{127}$  (2 -  $2^{23}$ )

which is approximately:

$$1.8 \times 10^{-38}$$

to  $3.40 \times 10^{-38}$

(integer comparison valid on IEEE FI.Pt. numbers of same sign!)

# **Basic Addition Algorithm**

For addition (or subtraction) this translates into the following steps:

- (1) compute Ye Xe (getting ready to align binary point)

- Xe-Ye

- (2) right shift Xm that many positions to form Xm 2

- (3) compute Xm 2 Xe-Ye + Ym

if representation demands normalization, then a normalization step follows:

- (4) left shift result, decrement result exponent (e.g., 0.001xx...) right shift result, increment result exponent (e.g., 101.1xx...) continue until MSB of data is 1 (NOTE: Hidden bit in IEEE Standard)

- (5) doubly biased exponent must be corrected:

$$Xe = 7$$

$Ye = -3$   $Ye = 0101$   $Ye = 0100$   $Ye = 0100$

extra subtraction step of the bias amount

(6) if result is 0 mantissa, may need to set the exponent to zero by special step

# **Extra Bits for rounding**

"Floating Point numbers are like piles of sand; every time you move one you lose a little sand, but you pick up a little dirt."

How many extra bits?

IEEE: As if computed the result exactly and rounded.

#### **Addition:**

| 1.xxxxx            | 1.xxxxx           | 1.xxxxx          |

|--------------------|-------------------|------------------|

| + <u>1.xxxxx</u>   | <u>0.001xxxxx</u> | <u>0.01xxxxx</u> |

| 1x.xxxxy           | 1.xxxxxyyy        | 1x.xxxxyyy       |

| post-normalization | pre-normalization | pre and post     |

- Guard Digits: digits to the right of the first p digits of significand to guard against loss of digits – can later be shifted left into first P places during normalization.

- Addition: carry-out shifted in

- Subtraction: borrow digit and guard

- Multiplication: carry and guard, Division requires guard

# **Rounding Digits**

normalized result, but some non-zero digits to the right of the significand --> the number should be rounded

one round digit must be carried to the right of the guard digit so that after a normalizing left shift, the result can be rounded, according to the value of the round digit

#### IEEE Standard:

four rounding modes: round to nearest (default) round towards plus infinity

round towards plus infinity round towards minus infinity

round towards 0

round to nearest:

round digit < B/2 then truncate

> B/2 then round up (add 1 to ULP: unit in last place)

= B/2 then round to nearest even digit

it can be shown that this strategy minimizes the mean error

cs 152 I7 Divide,FP. 29 troduced by rounding

DAP ©UCB 1997

# **Sticky Bit**

Additional bit to the right of the round digit to better fine tune rounding

#### Rounding Summary:

Radix 2 minimizes wobble in precision

Normal operations in +,-,\*,/ require one carry/borrow bit + one guard digit

One round digit needed for correct rounding

Sticky bit needed when round digit is B/2 for max accuracy

Rounding to nearest has mean error = 0 if uniform distribution of digits are assumed

generates a borrow

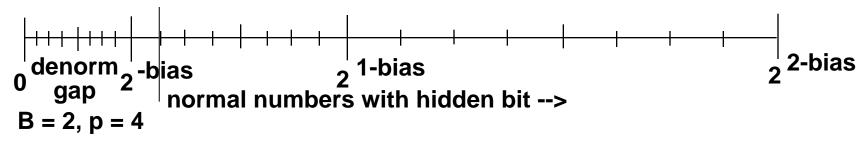

#### **Denormalized Numbers**

The gap between 0 and the next representable number is much larger than the gaps between nearby representable numbers.

IEEE standard uses denormalized numbers to fill in the gap, making the distances between numbers near 0 more alike.

same spacing, half as many values!

NOTE: PDP-11, VAX cannot represent subnormal numbers. These machines underflow to zero instead.

# **Infinity and NaNs**

result of operation *overflows*, i.e., is larger than the largest number that can be represented

overflow is not the same as divide by zero (raises a different exception)

It may make sense to do further computations with infinity e.g., X/0 > Y may be a valid comparison

Not a number, but not infinity (e.q. sqrt(-4)) invalid operation exception (unless operation is = or  $\neq$ )

NaN S 1 . . . 1 non-zero HW decides what goes here

NaNs propagate: f(NaN) = NaN

# **Pentium Bug**

- Pentium FP Divider uses algorithm to generate multiple bits per steps

- FPU uses most significant bits of divisor & dividend/remainder to guess next 2 bits of quotient

- Guess is taken from lookup table: -2, -1,0,+1,+2 (if previous guess too large a reminder, quotient is adjusted in subsequent pass of -2)

- Guess is multiplied by divisor and subtracted from remainder to generate a new remainder

- Called SRT division after 3 people who came up with idea

- $^{\circ}$  Pentium table uses 7 bits of remainder + 4 bits of divisor =  $2^{11}$  entries

- 5 entries of divisors omitted: 1.0001, 1.0100, 1.0111, 1.1010, 1.1101 from PLA (fix is just add 5 entries back into PLA: cost \$200,000)

- Self correcting nature of SRT => string of 1s must follow error

- e.g., 1011 1111 1111 1111 1011 1000 0010 0011 0111 1011 0100 (2.99999892918)

- Since indexed also by divisor/remainder bits, sometimes bug doesn't show even with dangerous divisor value

cs 152 I7 Divide,FP.30 DAP ©UCB 1997

# Pentium bug appearance

- First 11 bits to right of decimal point always correct: bits 12 to 52 where bug can occur (4th to 15th decimal digits)

- ° FP divisors near integers 3, 9, 15, 21, 27 are dangerous ones:

- $3.0 > d \ge 3.0 36 \times 2^{-22}$ ,  $9.0 > d \ge 9.0 36 \times 2^{-20}$

- 15.0 > d  $\geq$  15.0 36 x 2<sup>-20</sup>, 21.0 > d  $\geq$  21.0 36 x 2<sup>-19</sup>

- 0.333333 x 9 could be problem

- ° In Microsoft Excel, try (4,195,835 / 3,145,727) \* 3,145,727

- = 4,195,835 => not a Pentium with bug

- = 4,195,<u>579</u> => Pentium with bug (assuming Excel doesn't already have SW bug patch)

- Rarely noticed since error in 5th significant digit

- Success of IEEE standard made discovery possible:

- ≈ all computers should get same answer

# Pentium Bug Time line

- June 1994: Intel discovers bug in Pentium: takes months to make change, reverify, put into production: plans good chips in January 1995 4 to 5 million Pentiums produced with bug

- Scientist suspects errors and posts on Internet in September 1994

- Nov. 22 Intel Press release: "Can make errors in 9th digit ... Most engineers and financial analysts need only 4 of 5 digits. Theoretical mathematician should be concerned. ... So far only heard from one."

- o Intel claims happens once in 27,000 years for typical spread sheet user:

- 1000 divides/day x error rate assuming numbers random

- Dec 12: IBM claims happens once per 24 days: Bans Pentium sales

- 5000 divides/second x 15 minutes =  $\frac{4,200,000}{4}$  divides/day

- IBM statement: http://www.ibm.com/Features/pentium.html

- Intel said it regards IBM's decision to halt shipments of its Pentium processor-based systems as unwarranted.

# Pentium jokes

° Q: What's another name for the "Intel Inside" sticker they put on Pentiums?

A: Warning label.

° Q: Have you heard the new name Intel has chosen for the Pentium?

A: the Intel Inacura.

° Q: According to Intel, the Pentium conforms to the IEEE standards for floating point arithmetic. If you fly in aircraft designed using a Pentium, what is the correct pronunciation of "IEEE"?

A: Aaaaaaaiiiiiiiiieeeeeeeeeee!

° TWO OF TOP TEN NEW INTEL SLOGANS FOR THE PENTIUM

9.9999973251 It's a FLAW, Dammit, not a Bug

7.9999414610 Nearly 300 Correct Opcodes

# Pentium conclusion: Dec. 21, 1994 \$500M write-off

"To owners of Pentium processor-based computers and the PC community:

We at Intel wish to sincerely apologize for our handling of the recently publicized Pentium processor flaw.

The Intel Inside symbol means that your computer has a microprocessor second to none in quality and performance. Thousands of Intel employees work very hard to ensure that this is true. But no microprocessor is ever perfect.

What Intel continues to believe is technically an extremely minor problem has taken on a life of its own. Although Intel firmly stands behind the quality of the current version of the Pentium processor, we recognize that many users have concerns.

We want to resolve these concerns.

Intel will exchange the current version of the Pentium processor for an updated version, in which this floating-point divide flaw is corrected, for any owner who requests it, free of charge anytime during the life of their computer. Just call 1-800-628-8686."

Sincerely, Andrew S. Grove President /CEO

Craig R. Barrett

Executive Vice President

&COO

Gordon E. Moore Chairman of the Board

# **Summary**

- Pentium: Difference between bugs that board designers must know about and bugs that potentially affect all users

- Why not make public complete description of bugs in later category?

- \$200,000 cost in June to repair design

- \$500,000,000 loss in December in profits to replace bad parts

- How much to repair Intel's reputation?

- What is technologists responsibility in disclosing bugs?

- Bits have no inherent meaning: operations determine whether they are really ASCII characters, integers, floating point numbers

- Divide can use same hardware as multiply: Hi & Lo registers in MIPS

- Floating point basically follows paper and pencil method of scientific notation using integer algorithms for multiply and divide of significands

- ° IEEE 754 requires good rounding; special values for NaN, Infinity

cs 152 I7 Divide,FP.35 DAP ©UCB 1997