module mod3a(clock, y, reset,z)

;

input clock ;

input y ;

input reset ;

output z ;

reg z;

reg [1:0] state;

always @ (posedge clock)

if (reset)

begin

state=0;

z=1;

end

else

if (y)

begin

state=state+1;

if (state==2'b11

)

begin

state=0;

z=1;

end

else

z=0;

end

endmodule

|

module mod3b(clock, y, reset,z)

input clock ;

input y ;

input reset ;

output z ;

reg [1:0]state;

assign z=~|state;

always @(posedge clock)

begin

if (reset)

state=0;

else

if (y)

if (state==2)

state=0;

else

state=state+1;

end

endmodule

|

module mod3f (clock, y, reset,

z) ;

input clock ;

input y ;

input reset ;

output z ;reg z;

reg [1:0]pstate, nstate;

always @ (posedge clock)

begin

if (reset)

begin

pstate=0;

end

else

pstate=nstate;

end

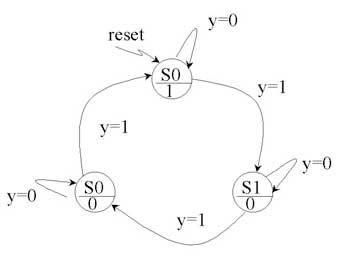

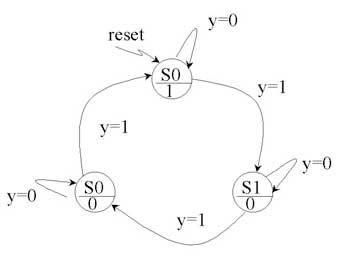

always @(pstate)

case(pstate)

0: begin z=1;

if (y) nstate=1;

else nstate=0;

end

1: begin z=0;

if (y) nstate=2;

else nstate=1;

end

2: begin z=0;

if (y) nstate=0;

elsenstate=2;

end

default : begin z=0;

nstate=0;

end

endcase

endmodule

|